# **DEDICATED MCU FAMILY**FOR TV/MONITOR APPLICATIONS

**DATABOOK**

1<sup>st</sup> EDITION

**APRIL 1994**

# USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein: 1. Life support devices or systems are those which (a) are 2. A critical component is any component of a life support intended for surgical implant into the body, or (b) support device or system whose failure to perform can reasonor sustain life, and whose failure to perform, when ably be expected to cause the failure of the life support properly used in accordance with instructions for use device or system, or to affect its safety or effectiveness. provided with the product, can be reasonably expected to result in significant injury to the user.

# **TABLE OF CONTENTS**

| INTRODUCTION        | Page 4 |

|---------------------|--------|

| GENERAL INDEX       | 10     |

| 8BIT MCUs           | 11     |

| 8/16 BIT MCUs       | 371    |

| ST9 INSTRUCTION SET | 665    |

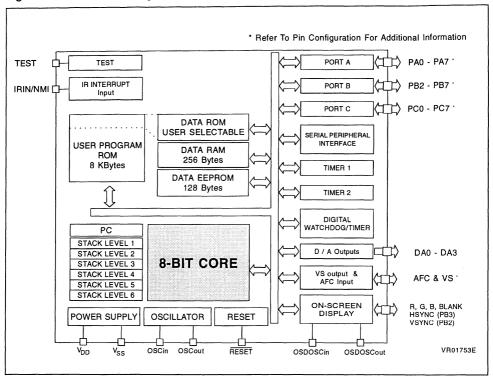

SGS-THOMSON's dedicated video product range is so extensive that it covers virtually all needs for the developers and producers of televisions, VCRs, monitors, satellite decoders and receivers and related applications. Devices for power and graphic circuits, and signal devices are found in the Video Products Databooks and Application Manuals. Complementing these products, and performing the central control functions and user interfaces of modern multistandard systems, SGS-THOMSON's dedicated microcontroller range for TV and Monitor has expanded to cover all model requirements, from low end TVs with Remote Control and On-Screen Display through Multi-Standard Monitors to high end TVs with Digital Data Slicers and expanded OSD capabilities for Closed Caption. As a result SGS-THOMSON has collected all these products into one book, as each microcontroller device is applicable for more than one area of use.

SGS-THOMSON's microcontrollers have two roots, the successful non-dedicated families for general applications, and secondly the company's capabilities in non-volatile memory technologies. Together with these, and with the experience brought from a long history of involvement in TV and Monitor applications, three families of dedicated microcontrollers have been developed, each with integrated features making them attractive and cost-effective system solutions.

These integrated functions bring features such as: on-chip EEPROM for parameter and channel storage; 14-bit Voltage Synthesizers on-chip for frequency tuning; On-Screen Displays (from 5 to 15 lines), also working together with Data Slicers for US Closed Caption; High current outputs for direct LED drive; inputs for immediate remote control commands; on-chip Digital to Analog converters for Analog controls and Sync Pulse Processing for determination of Video Standards, and a module for automatic East-West Pin Cushion Correction. Completing and adding to the dedicated functions is the flexibility that only a microcontroller-based system can offer.

For examples of full solutions based on microcontrollers, ask your local marketing for details of a series of complete chassis, with software (see table), fully available for evaluation of both the microcontroller functions and those of the dedicated power and signal products from SGS-THOMSON.

## Standard Software Packages For Standard Chassis

| SOFTWARE NAME | MCU    | FS<br>TUNING | VS<br>TUNING | TEL<br>CHIP         | ETEXT<br>BASIC | ТОР | FLOP1.5/<br>LIST | X26 | VIDEO<br>PROCESSOR    | OSD<br>STYLE | AVAILA<br>CHASSIS |       |

|---------------|--------|--------------|--------------|---------------------|----------------|-----|------------------|-----|-----------------------|--------------|-------------------|-------|

| BRIGITTE      | ST6356 | NO           | YES          | STV5345+<br>SAA5231 | 4Pgs           | NO  | NO               | NO  | TDA8217<br>PAL        | SIMPLE       | NOW               | NOW   |

| CRISTINA      | ST6367 | NO           | YES          | STV5345+<br>SAA5231 | 4Pgs           | NO  | NO               | NO  | STV2110A<br>PAL/SECAM | SIMPLE       | NOW               | NOW   |

|               | ST6367 | NO           | YES          | STV5345+<br>SAA5231 | 4Pgs           | NO  | NO               | NO  | STV2102A<br>PAL       | SIMPLE       | NOW               | NOW   |

| DORA          | ST6387 | NO           | YES          | STV5345+<br>SAA5231 | NO             | NO  | 8Pgs             | YES | STV2110A<br>PAL/SECAM | SIMPLE       | Q4/93             | Q4/93 |

Consult your SGS-THOMSON marketing contact for an update on this chart

# ST636x ROM Devices. MCU For TV Tuning with On-Screen Display

| DEVICE | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | AFC | vs  | D/A | COLOUR<br>PINS | EMULATING<br>DEVICES |

|--------|----------------|----------------|-------------------|-----|-----|-----|----------------|----------------------|

| ST6365 | 8K             | 256            | 384               | YES | YES | 4   | 3              | ST63E85, ST63T85     |

| ST6367 | 8K             | 256            | 384               | YES | YES | 6   | 3              | ST63E87, ST63T87     |

| ST6375 | 14K            | 256            | 384               | YES | YES | 4   | 3              | ST63E85, ST63T85     |

| ST6377 | 14K            | 256            | 384               | YES | YES | 6   | 3              | ST63E87, ST63T87     |

| ST6385 | 20K            | 256            | 384               | YES | YES | 4   | 3              | ST63E85, ST63T85     |

| ST6387 | 20K            | 256            | 384               | YES | YES | 6   | 3              | ST63E87, ST63T87     |

# ST63E6x EPROM/OTP Devices. MCU For TV Tuning with On-Screen Display

| DEVICE  | EPROM<br>(Bytes) | OTPROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | AFC | vs  | D/A | COLOUR<br>PINS | TARGET<br>ROM DEVICES |

|---------|------------------|-------------------|----------------|-------------------|-----|-----|-----|----------------|-----------------------|

| ST63E85 | 20K              |                   | 256            | 384               | YES | YES | 4   | 3              | ST6365, 75, 85        |

| ST63T85 |                  | 20K               | 256            | 384               | YES | YES | 4   | 3              | ST6365, 75, 85        |

| ST63E87 | 20K              |                   | 256            | 384               | YES | YES | 6   | 3              | ST6367, 77 87         |

| ST63T87 |                  | 20K               | 256            | 384               | YES | YES | 6   | 3              | ST6367, 77, 87        |

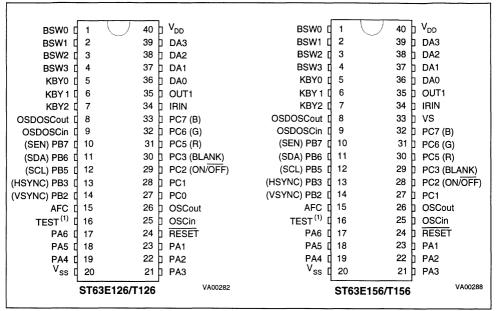

# ST631xx ROM Devices. MCU For TV Frequency and Voltage Synthesis with On-Screen Display

| DEVICE  | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | VO | KBY<br>I/O | BSW<br>OUT | AFC | vs  | D/A | PACK.  | EMUL.<br>DEVICES |

|---------|----------------|----------------|-------------------|----|------------|------------|-----|-----|-----|--------|------------------|

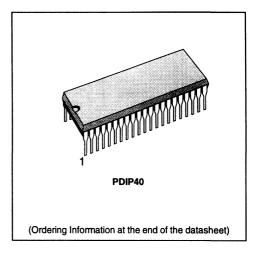

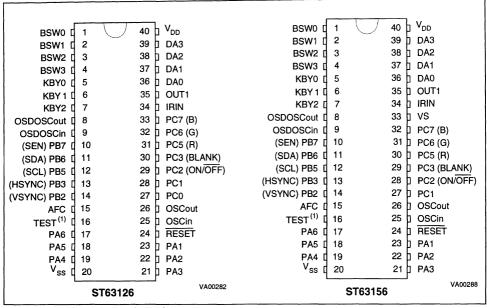

| ST63126 | 8K             | 256            | 128               | 12 | 3          | 4          | YES | NO  | 4   | PDIP40 | ST63E126         |

| ST63156 | 8K             | 256            | 128               | 11 | 3          | 4          | YES | YES | 4   | PDIP40 | ST63E156         |

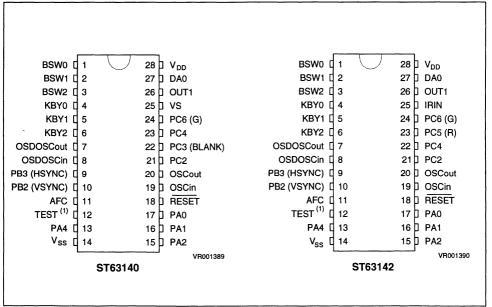

| ST63140 | 8K             | 256            | 128               | 6  | 3          | 3          | YES | YES | 1   | PDIP28 | ST63E140         |

| ST63142 | 8K             | 256            | 128               | 6  | 3          | 3          | YES | NO  | 1   | PDIP28 | ST63E142         |

# ST631xx EPROM/OTP Devices. MCU For TV Frequency and Voltage Synthesis with On-Screen Display

|          |         |            |         |         |     | Т          |     | T   |     |     |        |               |

|----------|---------|------------|---------|---------|-----|------------|-----|-----|-----|-----|--------|---------------|

| DEVICE   | EPROM   | OTP<br>ROM | RAM     | EEPROM  | I/O | KBY<br>I/O | BSW | AFC | vs  | D/A | PACK.  | TARGET<br>ROM |

|          | (Bytes) | (Bytes)    | (Bytes) | (Bytes) |     |            |     |     |     |     |        | DEVICES       |

| ST63E140 | 8K      |            | 256     | 128     | 6   | 3          | 3   | YES | YES | 1   | PDIP28 | ST63140       |

| ST63T140 |         | 8K         | 256     | 128     | 6   | 3          | 3   | YES | YES | 1   | PDIP28 | ST63140       |

| ST63E142 | 8K      |            | 256     | 128     | 6   | 3          | 3   | YES | NO  | 1   | PDIP28 | ST63142       |

| ST631T42 |         | 8K         | 256     | 128     | 6   | 3          | 3   | YES | NO  | 1   | PDIP28 | ST63142       |

| ST63E126 | 8K      |            | 256     | 128     | 12  | 3          | 4   | YES | NO  | 4   | PDIP40 | ST63126       |

| ST63T126 |         | 8K         | 256     | 128     | 12  | 3          | 4   | YES | NO  | 4   | PDIP40 | ST63126       |

| ST63E156 | 8K      |            | 256     | 128     | 11  | 3          | 4   | YES | YES | 4   | PDIP40 | ST63156       |

| ST63T156 |         | 8K         | 256     | 128     | 11  | 3          | 4   | YES | YES | 4   | PDIP40 | ST63156       |

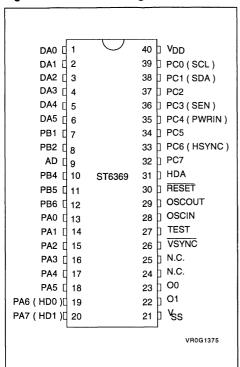

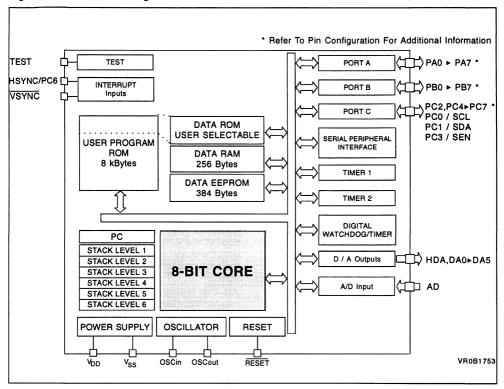

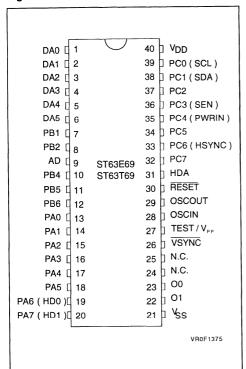

# ST6369 ROM Device. MCU For Digital Controlled Multi-Frequency Monitor

| DEVICE | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | A/D | 14-bit<br>D/A | 6-bit<br>D/A | EMULATING<br>DEVICES |

|--------|----------------|----------------|-------------------|-----|---------------|--------------|----------------------|

| ST6369 | 8K             | 256            | 384               | 1   | 1             | 6            | ST63E69, ST63T69     |

# ST6369 EPROM/OTP Device. MCU For Digital Controlled Multi-Frequency Monitor

| DEVICE  | EPROM<br>(Bytes) | OTPROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | A/D | 14-bit<br>D/A | 6-bit<br>D/A | TARGET<br>ROM DEVICE |

|---------|------------------|-------------------|----------------|-------------------|-----|---------------|--------------|----------------------|

| ST63E69 | 8K               |                   | 256            | 384               | 1   | 1             | 6            | ST6369               |

| ST63T69 |                  | 8K                | 256            | 384               | 1   | 1             | 6            | ST6369               |

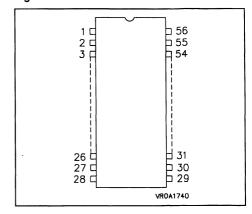

# ST7271 ROM Device. MCU For Digital Controlled Multi-Frequency Monitor

| DEVICE   | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | D/A Co<br>12-bit |    |   | 1 |         | Timer            | Package | EMULATING<br>DEVICES* |

|----------|----------------|----------------|-------------------|------------------|----|---|---|---------|------------------|---------|-----------------------|

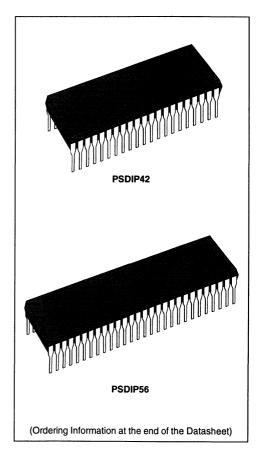

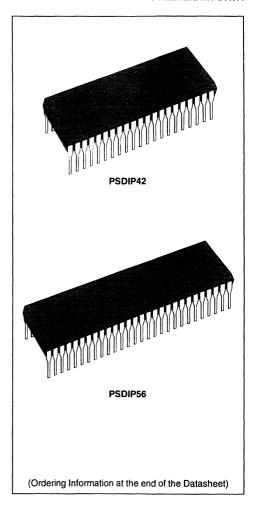

| ST7271N5 | 16K            | 256            | 512               | 2                | 14 | 1 | 1 | PSDIP56 | ST72E71, ST72T71 |         |                       |

| ST7271J1 | 16K            | 256            | 512               | 2                | 10 | 1 | 1 | PSDIP42 | ST72E71, ST72T71 |         |                       |

<sup>\*</sup> Note. Contact SGS-THOMSON Marketing for further information.

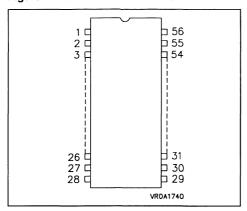

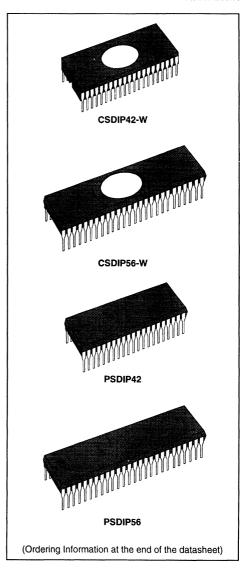

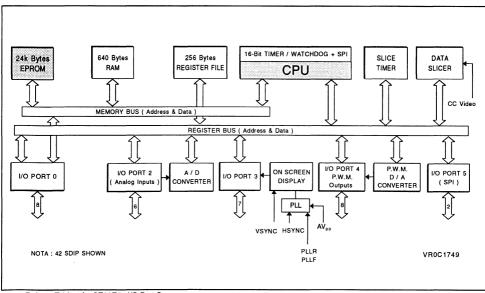

# ST929x ROM Devices. With On-Screen Display and SPI

| DEVICE               | ROM<br>(Bytes) | RAM<br>(Bytes) | I/O      | A/D | D/A Co<br>8-bit | nverter<br>14-bit | Data<br>Slicer | Timer  | Package            | EMULATING<br>DEVICES*  |

|----------------------|----------------|----------------|----------|-----|-----------------|-------------------|----------------|--------|--------------------|------------------------|

| ST9291N6<br>ST9291J6 | 32K<br>32K     | 640<br>640     | 42<br>32 | 1   | 8<br>8          | 1                 | -              | 2<br>2 | PSDIP56<br>PSDIP42 | ST92E91N6<br>ST92E91J6 |

| ST9293J7             | 48K            | 768            | 31       | 1   | -               | -                 | -              | 2      | PSDIP42            | ST92E93J7              |

| ST9294N6<br>ST9294J6 | 32K<br>32K     | 640<br>640     | 42<br>31 | 1   | 8<br>8          | -                 | 1              | 2<br>2 | PSDIP56<br>PSDIP42 | ST92E91N6<br>ST92E94J6 |

# ST92E9x EPROM Devices. With On-Screen Display and SPI

| DEVICE                 | EPROM<br>(Bytes) | RAM<br>(Bytes) | 1/0      | A/D    | D/A Co<br>8-bit | nverter<br>14-bit | Data<br>Slicer | Timer  | Package              | EMULATING<br>DEVICES* |

|------------------------|------------------|----------------|----------|--------|-----------------|-------------------|----------------|--------|----------------------|-----------------------|

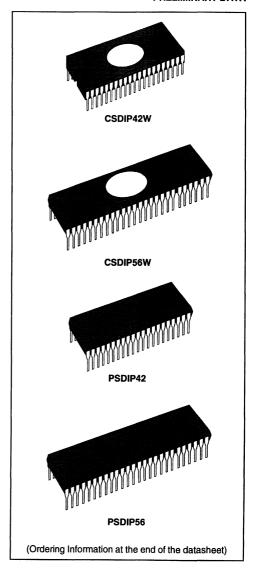

| ST92E91N6<br>ST92E91J6 | 32K<br>32K       | 640<br>640     | 42<br>32 | 1      | 8<br>8          | 1                 | -              | 2<br>2 | CSDIP56W<br>CSDIP42W | ST9291N6<br>ST9291J6  |

| ST92E93J7              | 48K              | 768            | 31       | 1      | -               | -                 | -              | 2      | CSDIP42W             | ST9293J7              |

| ST92E94N6<br>ST92E94J6 | 32K<br>32K       | 640<br>640     | 42<br>31 | 1<br>1 | 8<br>8          | -                 | 1<br>1         | 2<br>2 | CSDIP56W<br>CSDIP42W | ST9291N6<br>ST9294J6  |

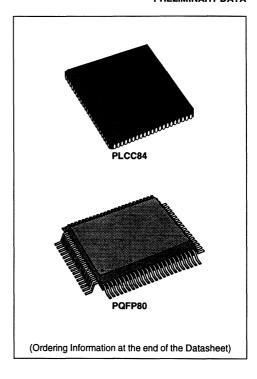

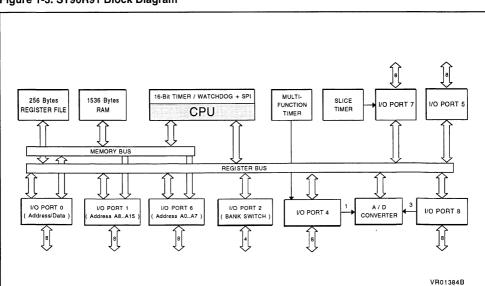

# ST90R5x, R9x ROMIess Devices. With Bankswitch and A/D Converter

| DEVICE                 | ROM<br>(Bytes) | RAM<br>(Bytes) | I/O<br>Port | A/D    | Timer  | SPI    | SCI | Package          |

|------------------------|----------------|----------------|-------------|--------|--------|--------|-----|------------------|

| ST90R51                | -              | -              | 54          | 1      | 4      | 1      | 2   | PQFP80           |

| ST90R91C1<br>ST90R91Q1 | -              | 1536<br>1536   | 35<br>40    | 1<br>1 | 3<br>3 | 1<br>1 | -   | PLCC68<br>PQFP80 |

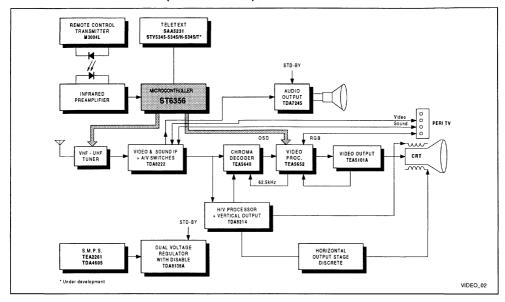

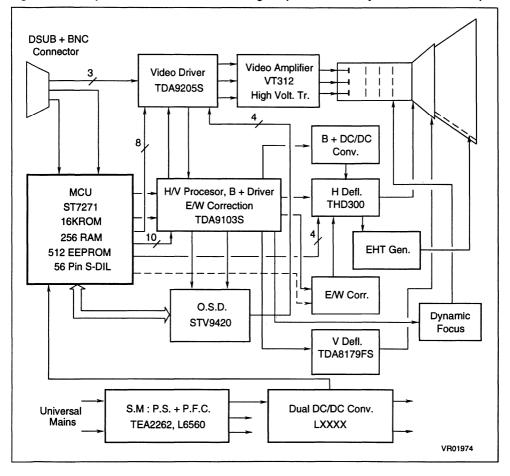

# PAL/SECAM low cost chassis (BG/DK standard)

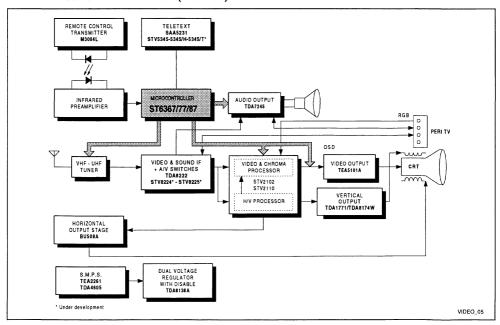

# PAL or PAL/SECAM color TV set (BG/DK/L)

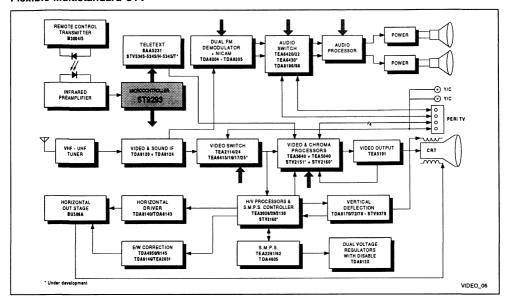

# Flexible Multistandard CTV

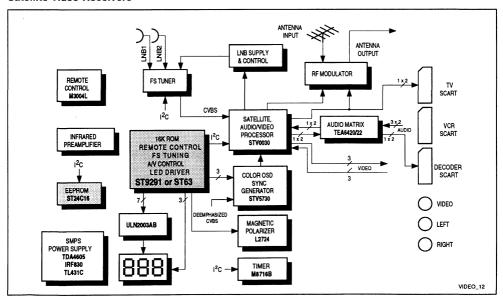

# Satellite video Receivers

# **GENERAL INDEX** —

# 8 Bit MCUs

| Type<br>Number                                                   | Function                                                              | Page |

|------------------------------------------------------------------|-----------------------------------------------------------------------|------|

| ST6365/75/85<br>ST6367/77/87                                     | 8-Bit HCMOS MCUs With On-Screen Display For TV Tuning,                | 12   |

| ST63E85/E87<br>ST63T85/T87                                       | 8-Bit EPROM HCMOS MCUs With On-Screen Display For TV Tuning           | 77   |

| ST6369                                                           | 8-Bit HCMOS MCU For Digital Controlled Multi Frequency Monitor        | 92   |

| ST63E69/T69                                                      | 8-Bit EPROM HCMOS MCU For Digital Controlled Multi Frequency Monitor  | 147  |

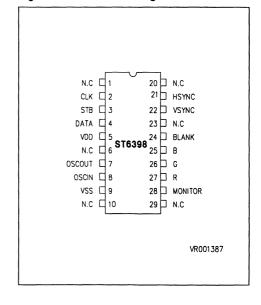

| ST6398                                                           | On Screen Display                                                     | 161  |

| ST63140/142<br>ST63126/156                                       | 8-Bit HCMOS MCUs For TV Frequency & Voltage Synthesis with OSD        | 190  |

| ST63E140/E142<br>ST63E126/E156<br>ST63T140/T142<br>ST63T126/T156 | 8-Bit EPROM HCMOS MCUs For TV Frequency & Voltage Synthesis with OSD  | 257  |

| ST7271                                                           | 8-Bit HCMOS MCUs with EEPROM and TV/MONITOR Dedicated Functions       | 273  |

| ST72E71                                                          | 8-Bit EPROM HCMOS MCUs With EEPROM and TV/MONITOR Dedicated Functions | 359  |

# 8/16 Bit MCUs

| Type<br>Number      | Function                                                                                 | Page |

|---------------------|------------------------------------------------------------------------------------------|------|

| ST9291              | 8-32k ROM HCMOS MCU with On Screen Display and Voltage Tuning Output                     | 373  |

| ST9293              | 48k ROM HCMOS MCUs With On Screen Display and A/D Converter                              | 392  |

| ST92E93/T93         | 48k 32k EPROM and OTP HCMOS MCUs With On Screen Display and Closed - Caption Data Slicer | 497  |

| ST9294              | 24k ROM HCMOS MCU With On Screen Display and Closed - Caption Data Slicer                | 513  |

| ST92E94/T94         | 24k EPROM HCMOS MCUs With On Screen Display and Closed - Caption Data Slicer             | 629  |

| ST90R50/51          | ROMLESS HCMOS MCU With Bankswitch and A/D Converter                                      | 647  |

| ST90R91             | ROMLESS HCMOS MCU With Bankswitch and A/D Converter                                      | 657  |

| ST9 Instruction Set | Reference Guide                                                                          | 665  |

# 8 Bit MCUs

# ST6365 DATASHEET INDEX

|                                              | Pages |

|----------------------------------------------|-------|

| ST6365, ST6375, ST6385                       |       |

| ST6367, ST6377, ST6387                       | . 1   |

| GENERAL DESCRIPTION                          | . 2   |

| PIN DESCRIPTION                              | . 4   |

| ST638x CORE                                  | . 6   |

| MEMORY SPACES                                | . 9   |

| INTERRUPT                                    | . 16  |

| RESET                                        |       |

| WAIT & STOP MODES                            |       |

| ON-CHIP CLOCK OSCILLATOR                     |       |

| INPUT/OUTPUT PORTS                           |       |

| TIMERS                                       |       |

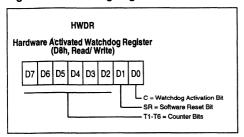

| HARDWARE ACTIVATED DIGITAL WATCHDOG FUNCTION | . 30  |

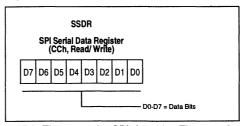

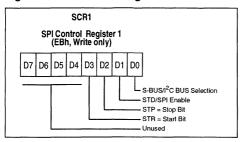

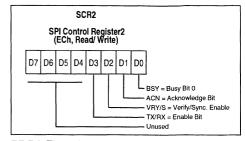

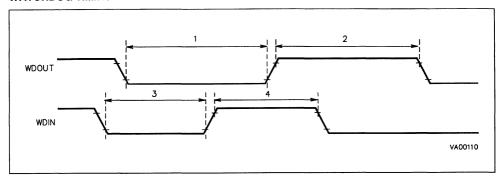

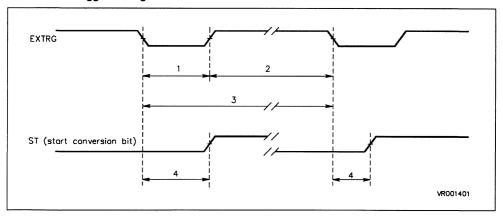

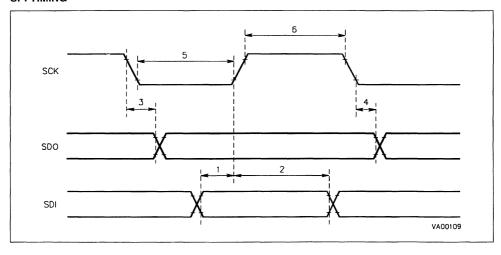

| SERIAL PERIPHERAL INTERFACE                  | . 31  |

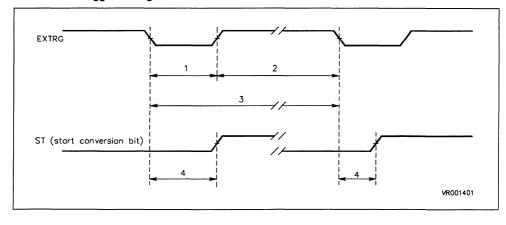

| 14-BIT VOLTAGE SYNTHESIS TUNING PERIPHERAL   | . 40  |

| 6-BIT PWM D/A CONVERTERS                     | . 41  |

| AFC A/D COMPARATOR                           |       |

| DEDICATED LATCHES                            |       |

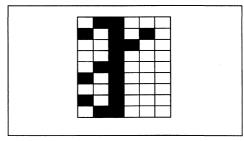

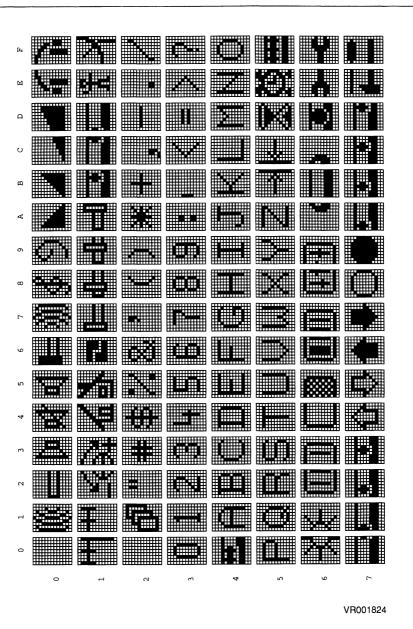

| ON-SCREEN DISPLAY (OSD)                      | . 43  |

| SOFTWARE DESCRIPTION                         | . 52  |

| ABSOLUTE MAXIMUM RATINGS                     | . 57  |

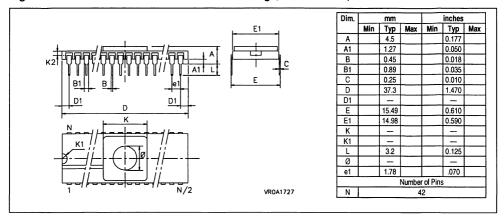

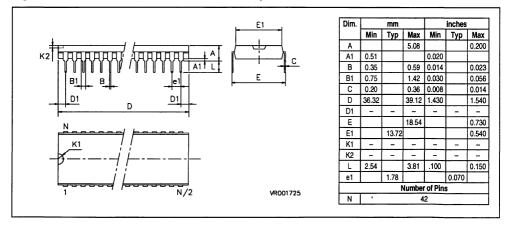

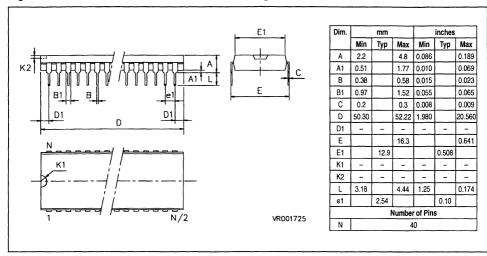

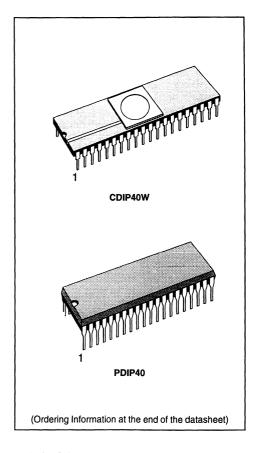

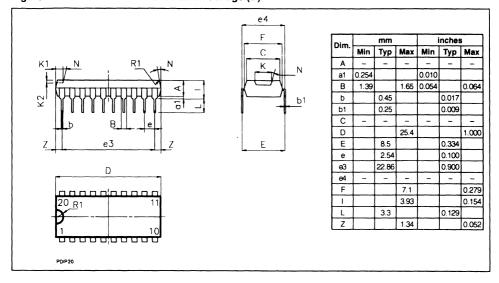

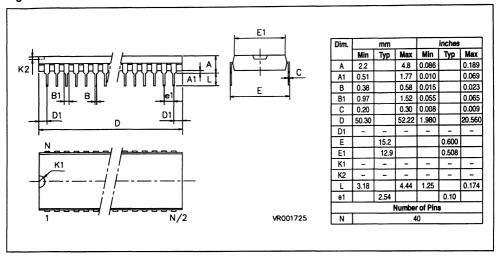

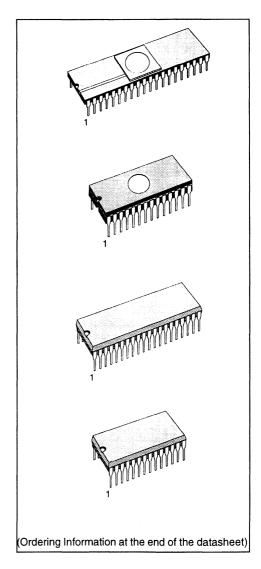

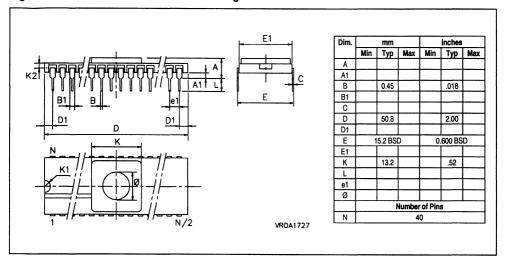

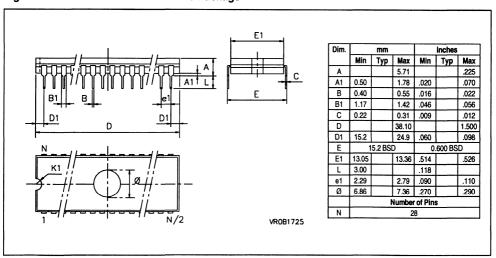

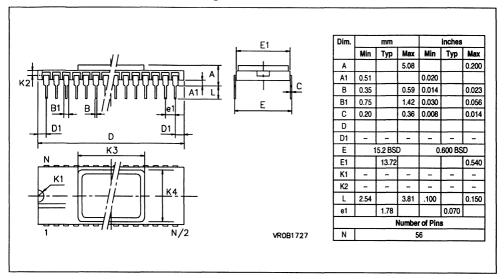

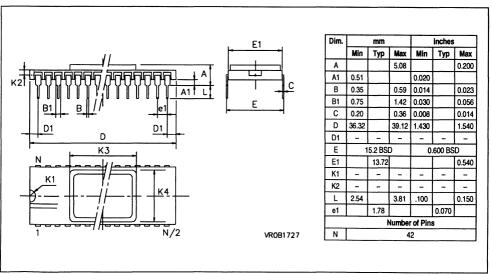

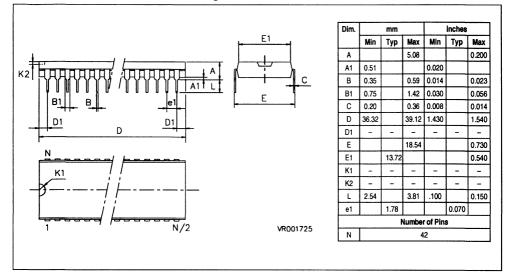

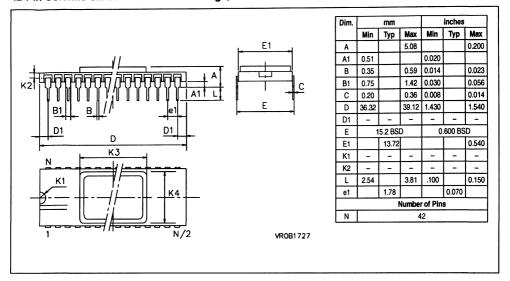

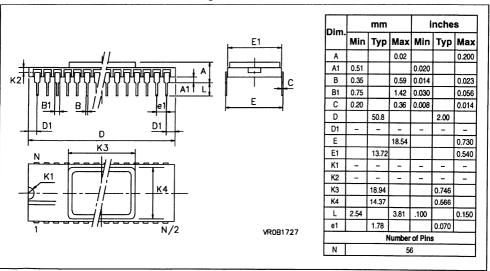

| PACKAGE MECHANICAL DATA                      | . 61  |

| ORDERING INFORMATION TABLE                   | . 63  |

| CTCOFOR TOR                                  |       |

| ST63E85, T85                                 |       |

| ST63E87, T87                                 | . 65  |

| GENERAL DESCRIPTION                          | . 66  |

| PIN DESCRIPTION                              |       |

| MEMORY SPACE                                 |       |

| EPROM/OTP DESCRIPTION                        |       |

| ABSOLUTE MAXIMUM RATINGS                     |       |

| PACKAGE MECHANICAL DATA                      |       |

| ORDERING INFORMATION                         |       |

| ORDERING INFORMATION TABLE                   |       |

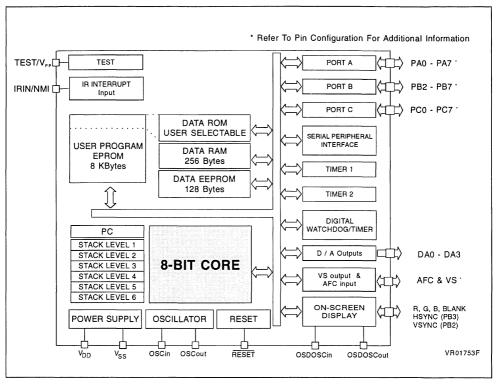

# ST6365, ST6375, ST6385 ST6367, ST6377, ST6387

# 8-BIT HCMOS MCUs WITH ON-SCREEN DISPLAY FOR TV TUNING

PRELIMINARY DATA

■ 4.5 to 6V supply operating range

8MHz Maximum Clock Frequency

User Program ROM: up to 20140 bytes

Reserved Test ROM: up to 340 bytes

Data ROM: user selectable size

Data RAM: 256 bytes

Data EEPROM: 384 bytes

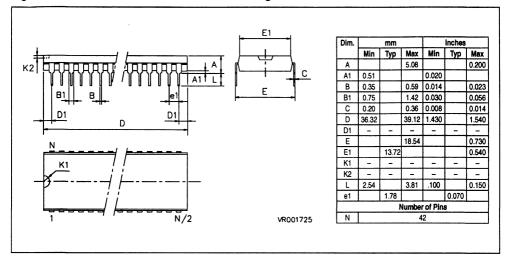

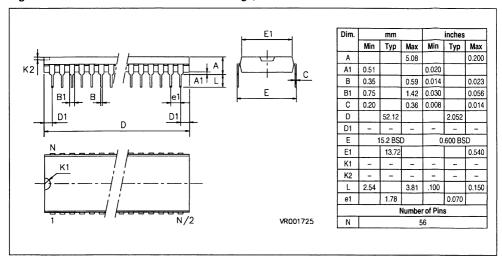

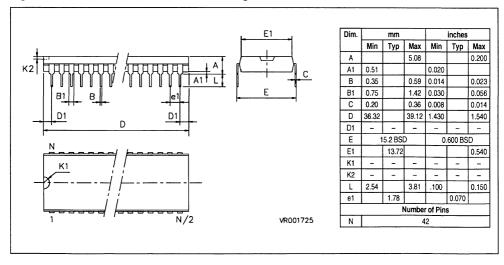

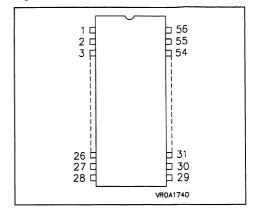

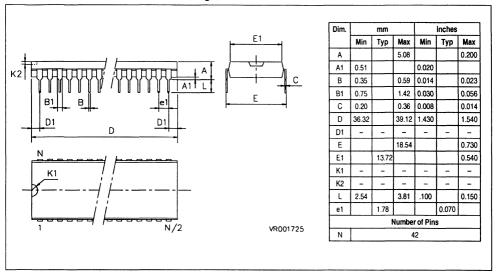

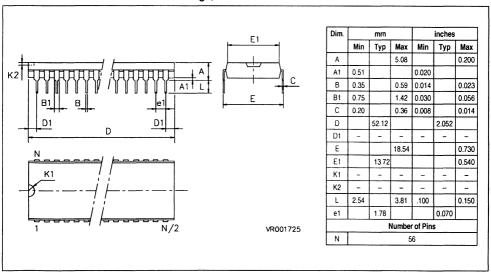

42-Pin Shrink Dual in Line Plastic Package

Up to 22 software programmable general purpose Inputs/Outputs, including 2 direct LED driving Outputs

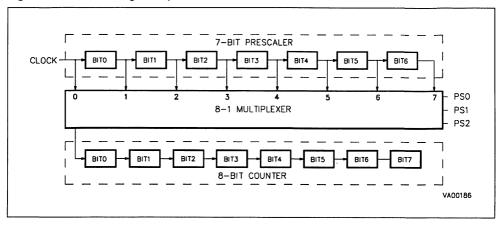

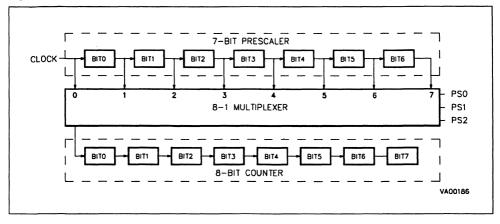

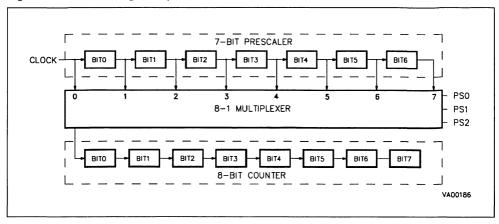

- Two Timers each including an 8-bit counter with a 7-bit programmable prescaler

- Digital Watchdog Function

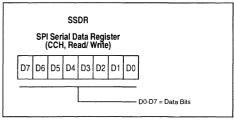

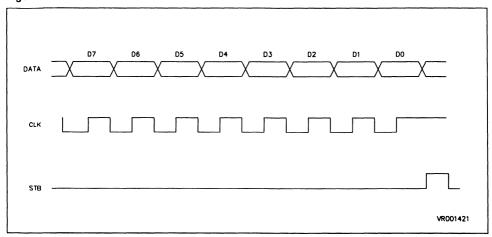

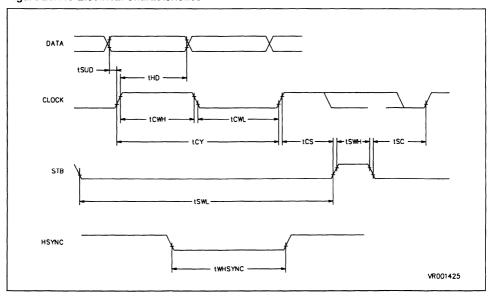

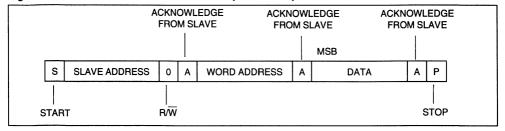

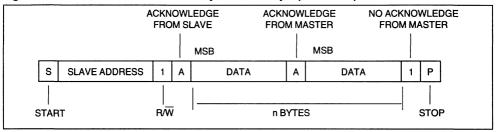

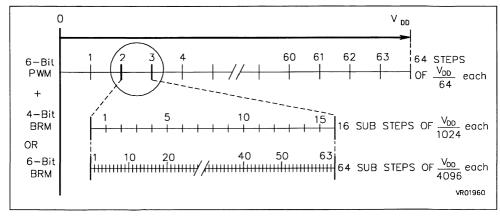

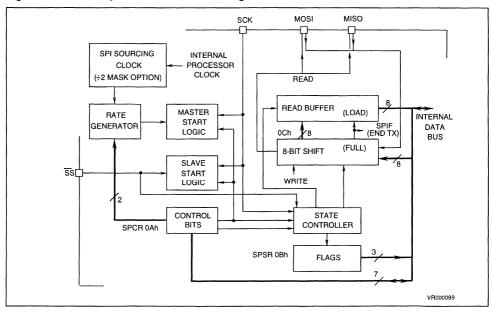

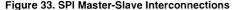

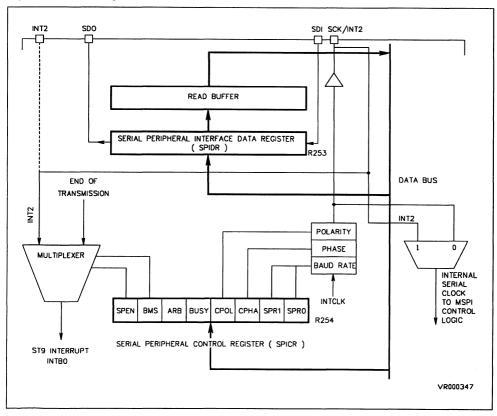

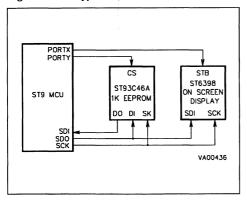

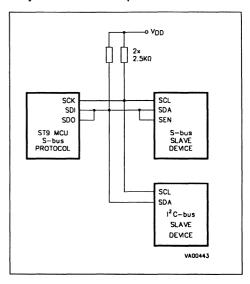

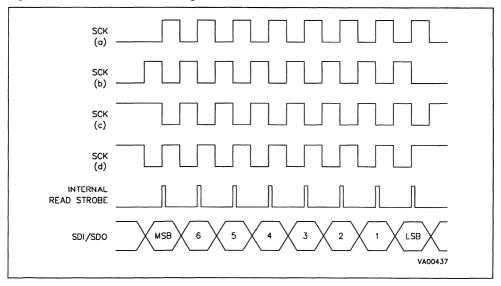

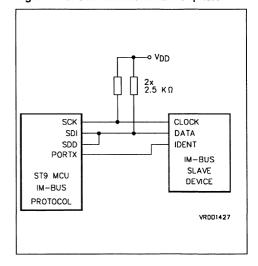

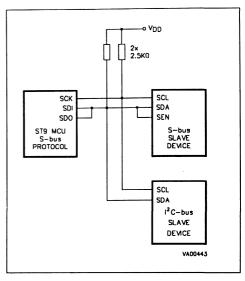

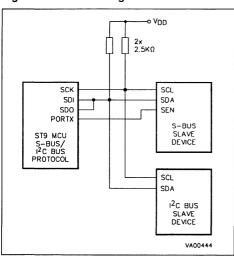

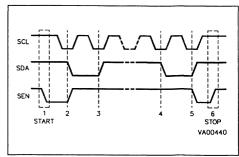

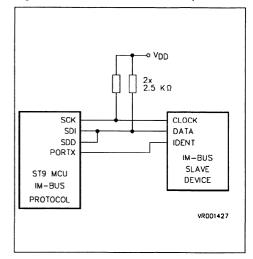

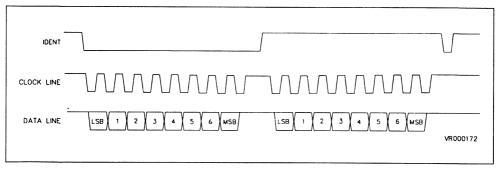

- Serial Peripheral Interface (SPI) supporting S-BUS/ I<sup>2</sup>C BUS and standard serial protocols

- SPI for external frequency synthesis tuning

- 14 bit counter for voltage synthesis tuning

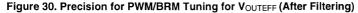

- Up to Six 6-Bit PWM D/A Converters

- AFC A/D converter with 0.5V resolution

- Five interrupt vectors (IRIN/NMI, Timer 1 & 2, VSYNC, PWR INT.)

- On-chip clock oscillator

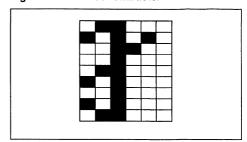

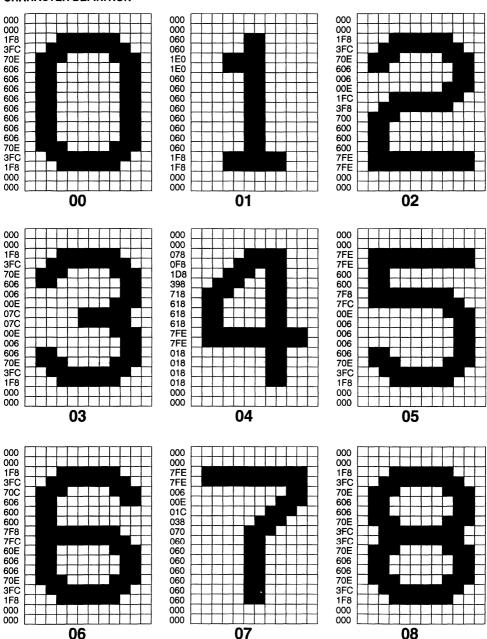

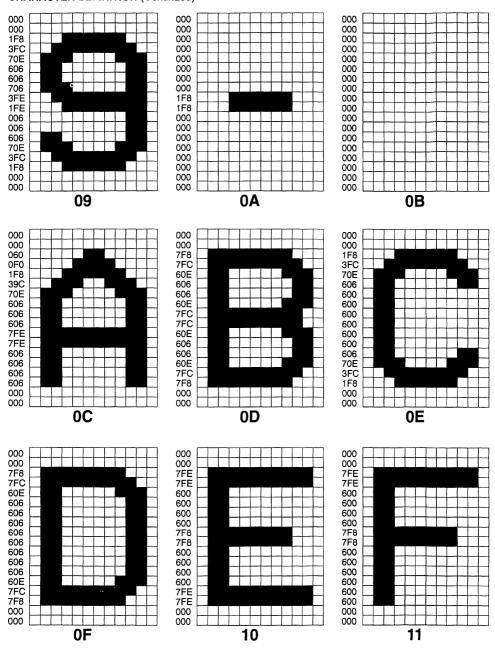

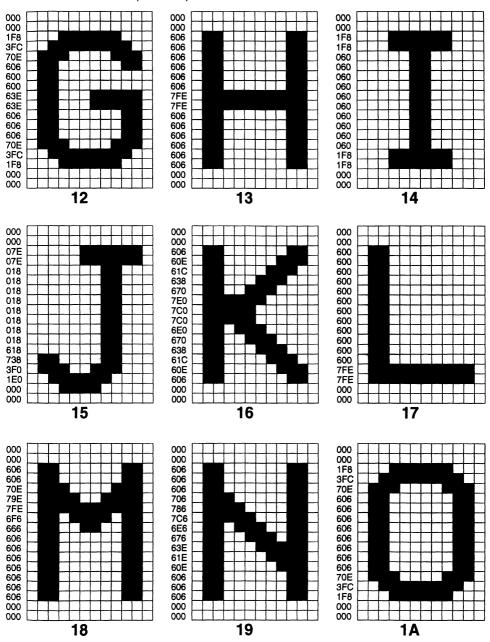

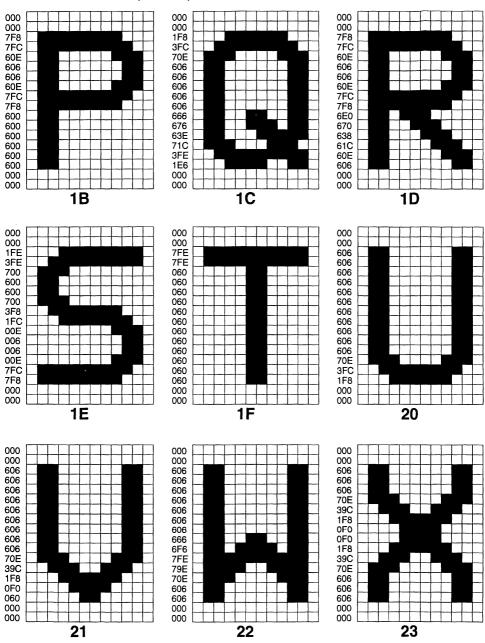

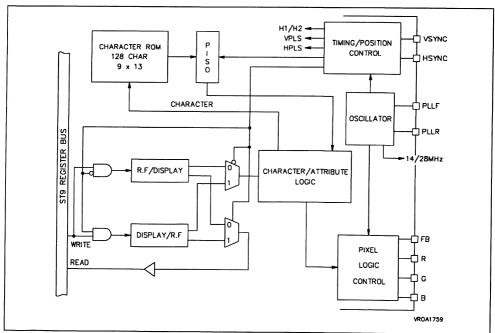

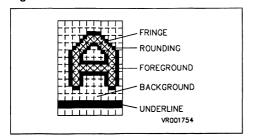

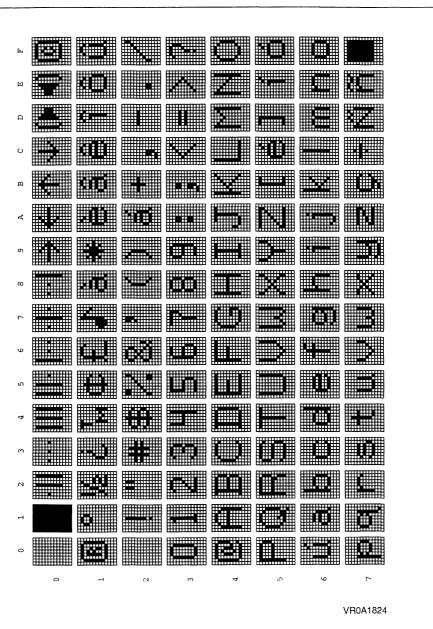

- 5 Lines by 15 Characters On-Screen Display Generator with 128 Characters

- All ROM types are supported by pin-to-pin EPROM, and OTP versions.

- The development tool of the ST636x,7x,8x microcontrollers consists of the ST638x-EMU emulation and development system to be connected via a standard RS232 serial line to an MS-DOS Personal Computer.

### **DEVICE SUMMARY**

| DEVICE | ROM<br>(Bytes) | D/A Converter |

|--------|----------------|---------------|

| ST6365 | 8K             | 4             |

| ST6367 | 8K             | 6             |

| ST6375 | 14K            | 4             |

| ST6377 | 14K            | 6             |

| ST6385 | 20K            | 4             |

| ST6387 | 20K            | 6             |

October 1993 1/79

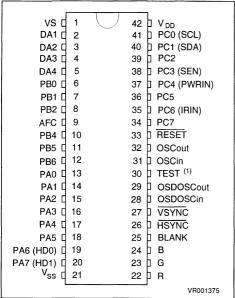

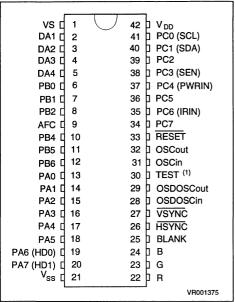

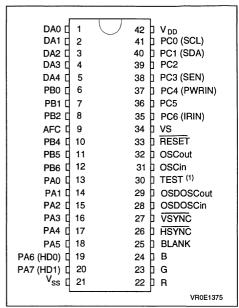

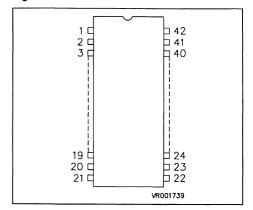

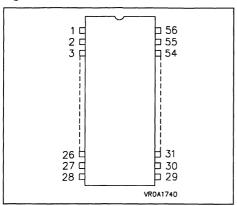

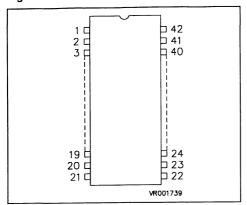

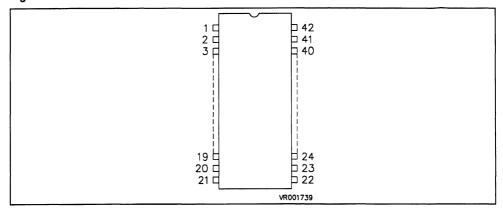

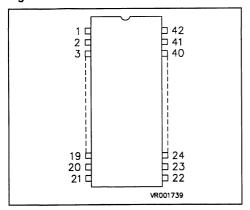

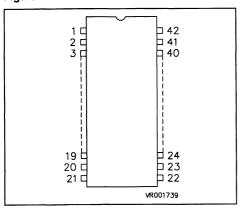

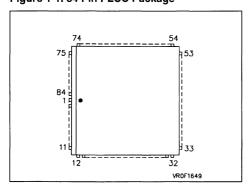

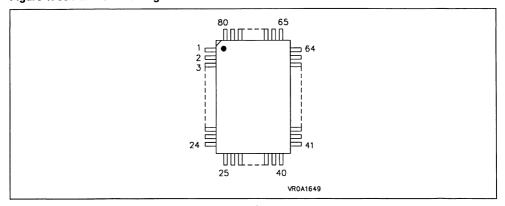

Figure 2. ST6365, 75, 85 Pin Configuration

Note 1. This pin is also the VPP input for EPROM based devices

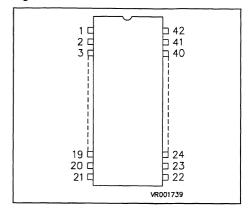

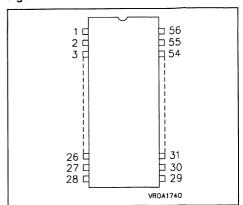

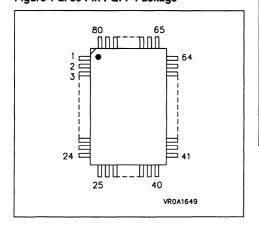

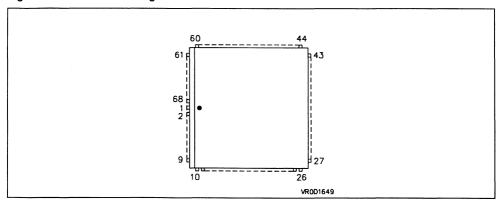

# Figure 1. ST6367, 77, 87 Pin Configuration

| İ | DA0                | 1  | 42 V <sub>DD</sub> |

|---|--------------------|----|--------------------|

| - | DA1 [              | 2  | 41 PC0 (SCL)       |

| 1 | DA2 [              | 3  | 40 PC1 (SDA)       |

|   | DA3 [              | 4  | 39 PC2             |

|   | DA4 🛭              | 5  | 38 PC3 (SEN)       |

|   | РВО [              | 6  | 37   PC4 (PWRIN)   |

| ļ | РВ1 🛚              | 7  | 36 PC5             |

| 1 | PB2 [              | 8  | 35 PC6 (IRIN)      |

| ı | AFC [              | 9  | 34 D VS            |

| 1 | PB4 [              | 10 | 33 RESET           |

|   | PB5 [              | 11 | 32 DSCout          |

| ١ | PB6 🛚              | 12 | 31 DSCin           |

|   | PAO [              | 13 | 30 TEST (1)        |

|   | PA1 [              | 14 | 29 DSDOSCout       |

| l | PA2 [              | 15 | 28 OSDOSCin        |

| ı | PA3 [              | 16 | 27 VSYNC           |

| 1 | PA4 [              | 17 | 26 HSYNC           |

|   | PA5 [              | 18 | 25 BLANK           |

| ١ | PA6 (HD0)          | 19 | 24 þ B             |

|   | PA7 (HD1)          | 20 | 23 þ G             |

| 1 | `V <sub>ss</sub> [ | 21 | 22 🕽 R             |

|   |                    |    | VR0E1375           |

## **GENERAL DESCRIPTION**

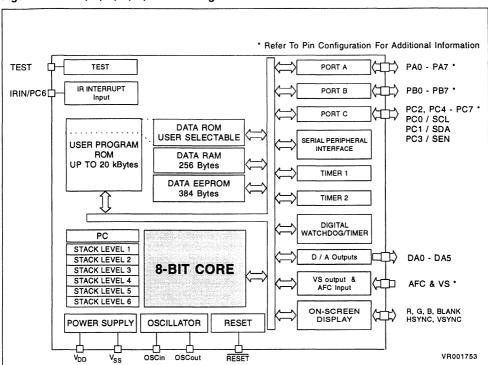

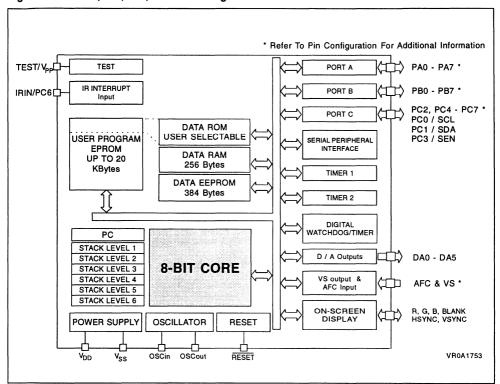

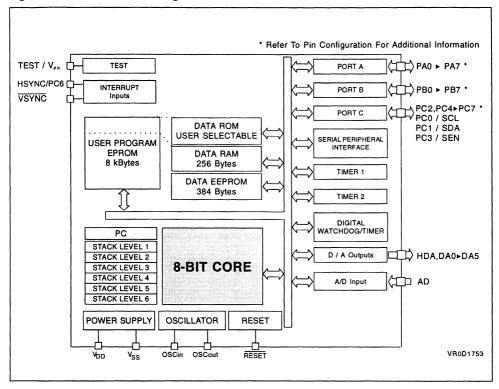

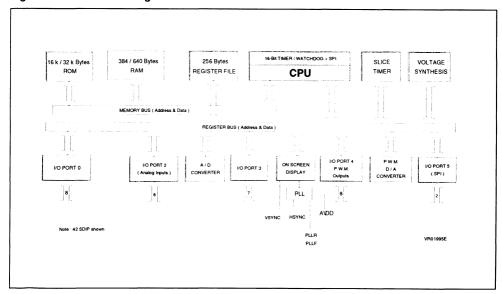

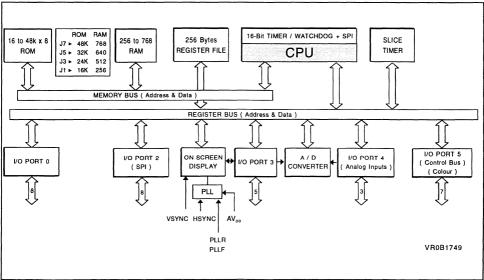

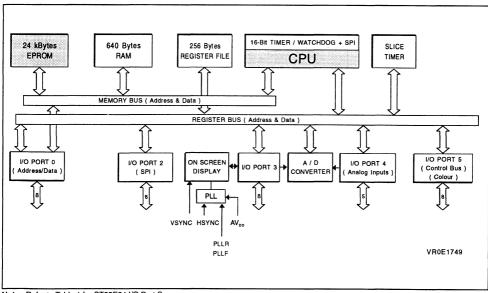

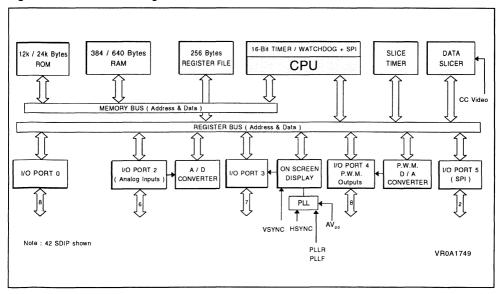

The ST6365,67,75,77,85,87 microcontrollers are members of the 8-bit HCMOS ST638x family, a series of devices specially oriented to TV applications. Different ROM size and peripheral configurations are available to give the maximum application and cost flexibility. All ST638x members are based on a building block approach: a common core is surrounded by a combination of on-chip peripherals (macrocells) available from a standard library. These peripherals are designed with the same Core technology providing full compatibility and short design time. Many of these macrocells are specially dedicated to TV applications. The macrocells of the ST638x family are: two Timer peripherals each including an 8-bit counter with a 7-bit software pro-

grammable prescaler (Timer), a digital hardware activated watchdog function (DHWD), a 14-bit voltage synthesis tuning peripheral, a Serial Peripheral Interface (SPI), up to six 6-bit PWM D/A converters, an AFC A/D converter with 0.5V resolution, an on-screen display (OSD) with 15 characters per line and 128 characters (in two banks each of 64 characters). In addition the following memory resources are available: program ROM (up to 20K), data RAM (256 bytes), EEPROM (384 bytes). Refer to pin configurations figures and to ST638x device summary (Table 1) for the definition of ST638x family members and a summary of differences among the different types.

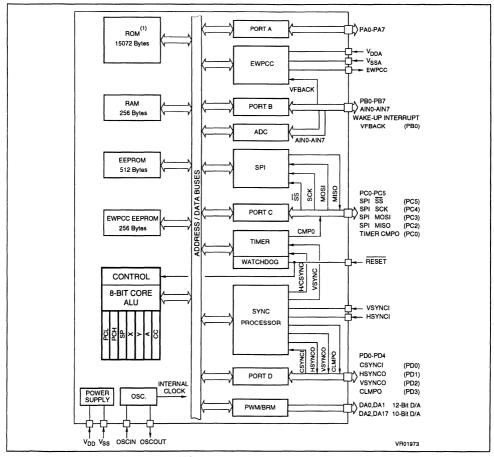

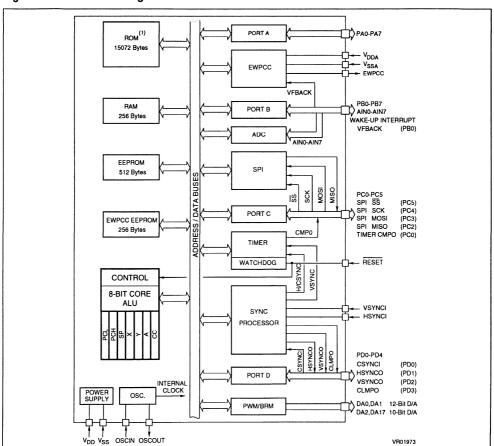

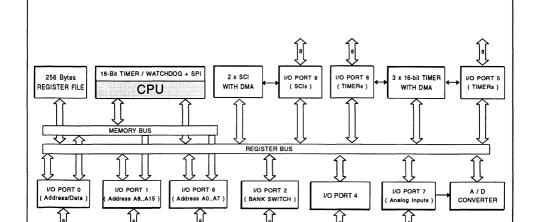

Figure 3. ST6365,67,75,77,85,87 Block Diagram

Table 1. Device Summary

| Table 1. Device o | able 1. Device Summary |                |                   |     |     |     |                |                      |

|-------------------|------------------------|----------------|-------------------|-----|-----|-----|----------------|----------------------|

| DEVICE            | ROM<br>(Bytes)         | RAM<br>(Bytes) | EEPROM<br>(Bytes) | AFC | vs  | D/A | COLOUR<br>PINS | EMULATING<br>DEVICES |

| ST6365            | 8K                     | 256            | 384               | YES | YES | 4   | 3              | ST63P85, ST63E85     |

| ST6367            | 8K                     | 256            | 384               | YES | YES | 6   | 3              | ST63P87, ST63E87     |

| ST6375            | 14K                    | 256            | 384               | YES | YES | 4   | 3              | ST63P85, ST63E85     |

| ST6377            | 14K                    | 256            | 384               | YES | YES | 6   | 3              | ST63P87, ST63E87     |

| ST6385            | 20K                    | 256            | 384               | YES | YES | 4   | 3              | ST63P85, ST63E85     |

| ST6387            | 20K                    | 256            | 384               | YES | YES | 6   | 3              | ST63P87, ST63E87     |

### PIN DESCRIPTION

$V_{DD}$  and  $V_{SS}$ . Power is supplied to the MCU using these two pins.  $V_{DD}$  is power and  $V_{SS}$  is the ground connection.

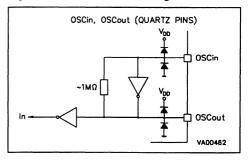

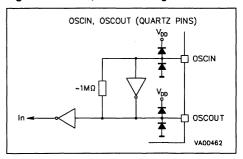

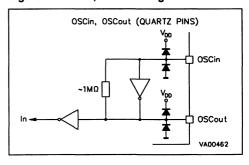

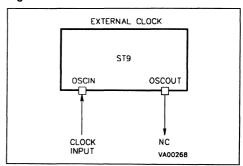

OSCin, OSCout. These pins are internally connected to the on-chip oscillator circuit. A quartz crystal or a ceramic resonator can be connected between these two pins in order to allow the correct operation of the MCU with various stability/cost trade-offs. The OSCin pin is the input pin, the OSCout pin is the output pin.

**RESET.** The active low RESET pin is used to start the microcontroller to the beginning of its program. Additionally the <u>quartz crystal</u> oscillator will be disabled when the RESET pin is low to reduce power consumption during reset phase.

**TEST.** The TEST pin must be held at V<sub>SS</sub> for normal operation.

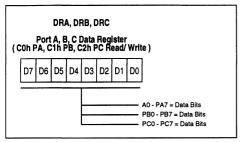

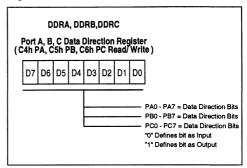

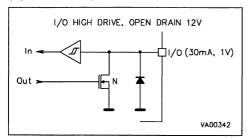

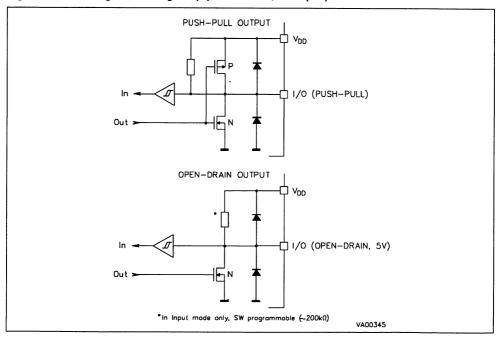

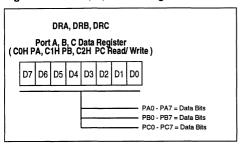

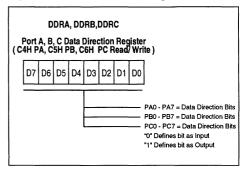

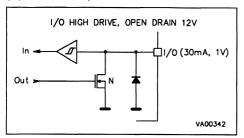

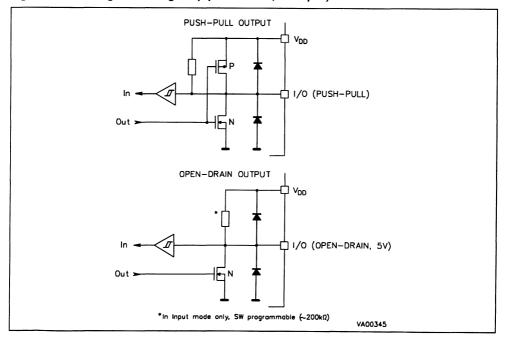

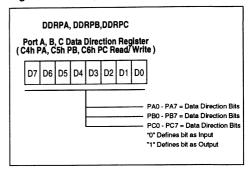

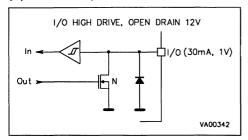

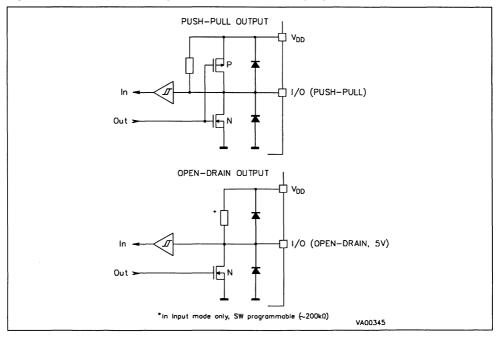

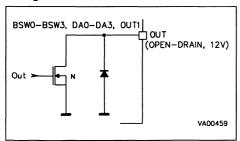

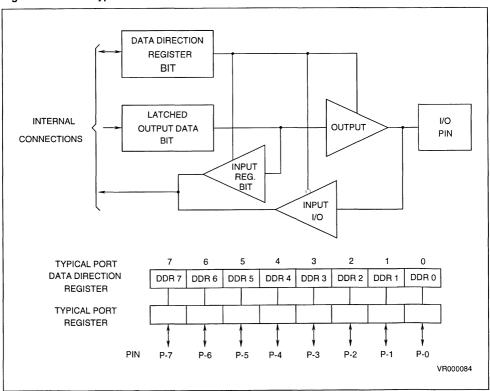

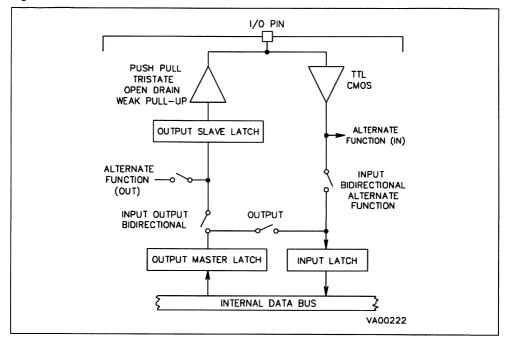

PA0-PA7. These 8 lines are organized as one I/O port (A). Each line may be configured as either an input with or without pull-up resistor or as an output under software control of the data direction register. Pins PA4 to PA7 are configured as open-drain outputs (12V drive). On PA4-PA7 pins the input pull-up option is not available while PA6 and PA7 have additional current driving capability (25mA, Vol:1V). PA0 to PA3 pins are configured as pushpull.

**PB0-PB2**, **PB4-PB6**. These 6 lines are organized as one I/O port (B). Each line may be configured as either an input with or without internal pull-up resistor or as an output under software control of the data direction register.

PC0-PC7. These 8 lines are organized as one I/O port (C). Each line may be configured as either an input with or without internal pull-up resistor or as an output under software control of the data direction register. Pins PC0 to PC3 are configured as open-drain (5V drive) in output mode while PC4 to PC7 are open-drain with 12V drive and the input pull-up options does not exist on these four pins.

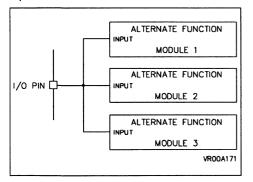

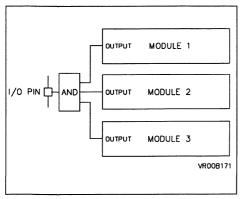

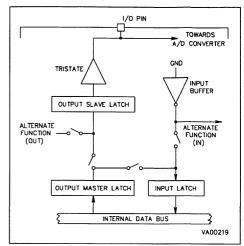

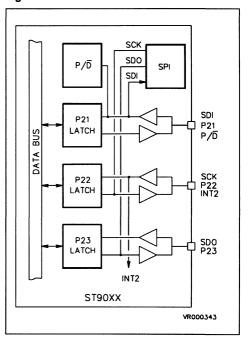

PC0, PC1 and PC3 lines when in output mode are "ANDed" with the SPI control signals and are all open-drain. PC0 is connected to the SPI clock signal (SCL), PC1 with the SPI data signal (SDA) while PC3 is connected with SPI enable signal (SEN, used in S-BUS protocol). Pin PC4 and PC6 can also be inputs to software programmable edge sensitive latches which can generate interrupts; PC4 can be connected to Power Interrupt while PC6 can be connected to the IRIN/NMI interrupt line.

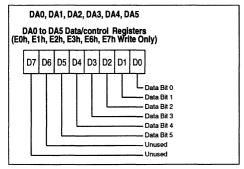

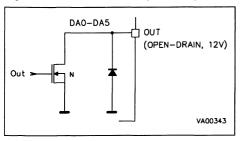

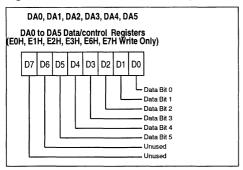

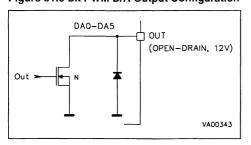

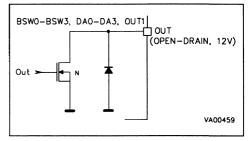

**DA0-DA5.** These pins are the six PWM D/A outputs of the 6-bit on-chip D/A converters. These lines have open-drain outputs with 12V drive. The output repetition rate is 31.25KHz (with 8MHz clock).

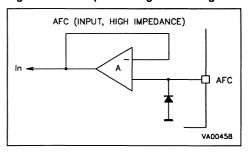

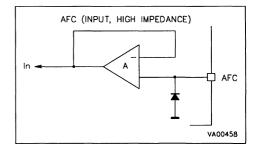

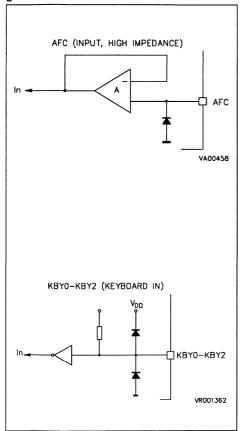

**AFC.** This is the input of the on-chip 10 levels comparator that can be used to implement the AFC function. This pin is an high impedance input able to withstand signals with a peak amplitude up to 12V.

**OSDOSCin, OSDOSCout.** These are the On Screen Display oscillator terminals. An oscillation capacitor and coil network have to be connected to provide the right signal to the OSD.

HSYNC, VSYNC. These are the horizontal and vertical synchronization pins. The active polarity of these pins to the OSD macrocell can be selected by the user as ROM mask option. If the device is specified to have negative logic inputs, then these signals are low the OSD oscillator stops. If the device is specified to have positive logic inputs, then when these signals are high the OSD oscillator stops. VSYNC is also connected to the VSYNC interrupt.

R, G, B, BLANK. Outputs from the OSD. R, G and B are the color outputs while BLANK is the blanking output. All outputs are push-pull. The active polarity of these pins can be selected by the user as ROM mask option.

VS. This is the output pin of the on-chip 14-bit voltage synthesis tuning cell (VS). The tuning signal present at this pin gives an approximate resolution of 40KHz per step over the UHF band. This line is a push-pull output with standard drive.

# Table 2. Pin Summary

| Pin Function                      | Description                                                               |  |  |

|-----------------------------------|---------------------------------------------------------------------------|--|--|

| DA0 to DA5                        | Output, Open-Drain, 12V                                                   |  |  |

| AFC                               | Input, High Impedance, 12V                                                |  |  |

| VS                                | Output, Push-Pull                                                         |  |  |

| R,G,B, BLANK                      | Output, Push-Pull                                                         |  |  |

| HSYNC, VSYNC                      | Input, Pull-up, Schmitt Trigger                                           |  |  |

| OSDOSCin                          | Input, High Impedance                                                     |  |  |

| OSDOSCout                         | Output, Push-Pull                                                         |  |  |

| TEST                              | Input, Pull-Down                                                          |  |  |

| OSCin                             | Input, Resistive Bias, Schmitt Trigger to Reset Logic Only                |  |  |

| OSCout                            | Output, Push-Pull                                                         |  |  |

| RESET                             | Input, Pull-up, Schmitt Trigger Input                                     |  |  |

| PA0-PA3                           | I/O, Push-Pull, Software Input Pull-up, Schmitt Trigger Input             |  |  |

| PA4-PA5                           | I/O, Open-Drain, 12V, No Input Pull-up, Schmitt Trigger Input             |  |  |

| PA6-PA7                           | I/O, Open-Drain, 12V, No Input Pull-up, Schmitt Trigger Input, High Drive |  |  |

| PB0-PB2                           | I/O, Push-Pull, Software Input Pull-up, Schmitt Trigger Input             |  |  |

| PB4-PB6                           | I/O, Push-Pull, Software Input Pull-up, Schmitt Trigger Input             |  |  |

| PC0-PC3                           | I/O, Open-Drain, 5V , Software Input Pull-up, Schmitt Trigger Input       |  |  |

| PC4-PC7                           | I/O, Open-Drain, 12V, No Input Pull-up, Schmitt Trigger Input             |  |  |

| V <sub>DD</sub> , V <sub>SS</sub> | Power Supply Pins                                                         |  |  |

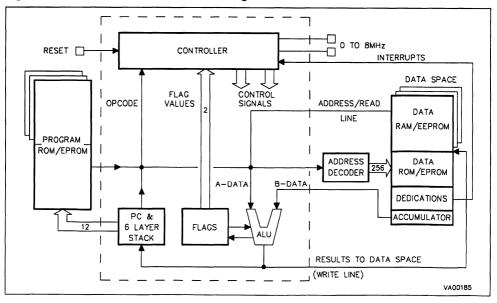

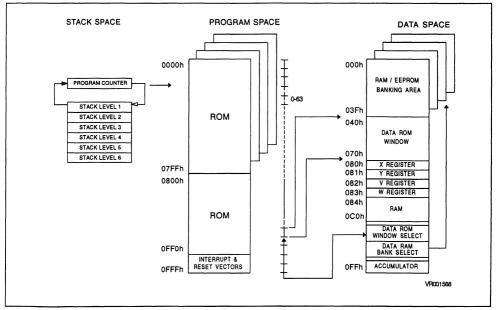

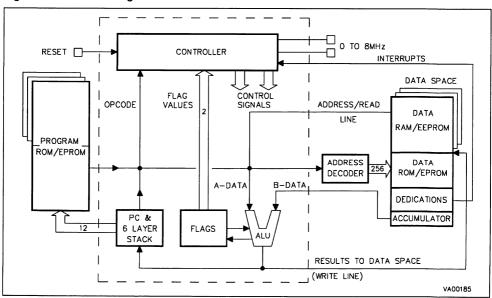

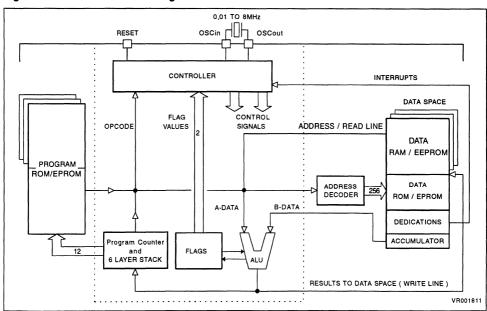

## ST638x CORE

The Core of the ST638x Family is implemented independently from the I/O or memory configuration. Consequently, it can be treated as an independent central processor communicating with I/O and memory via internal addresses, data, and control busses. The in-core communication is arranged as shown in the following block diagram figure; the controller being externally linked to both the reset and the oscillator, while the core is linked to the dedicated on-chip macrocells peripherals via the serial data bus and indirectly for interrupt purposes through the control registers.

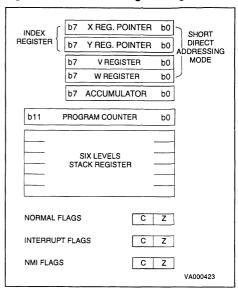

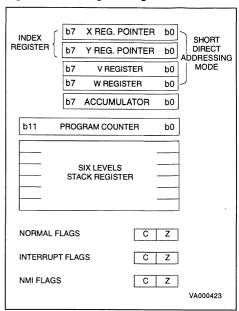

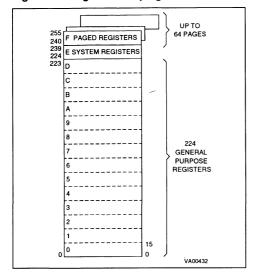

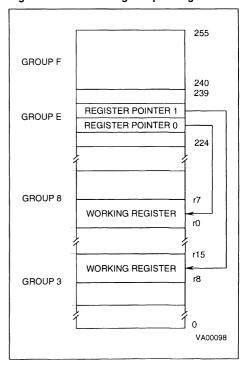

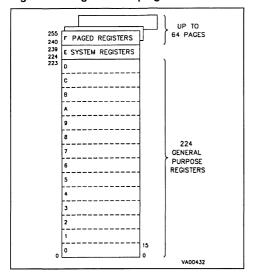

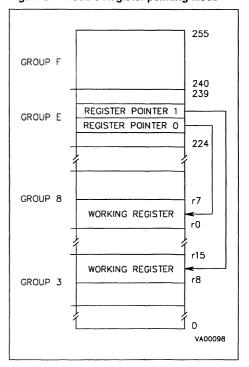

# Registers

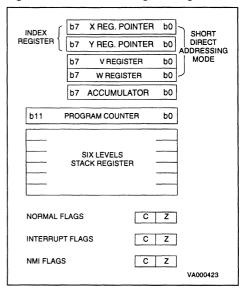

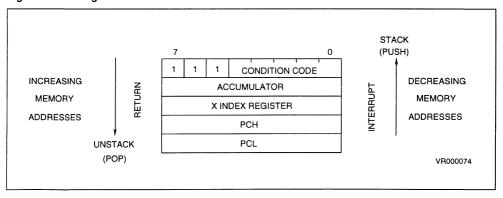

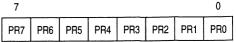

The ST638x Family Core has five registers and three pairs of flags available to the programmer. They are shown in Figure 5 and are explained in the following paragraphs together with the program and data memory page registers.

**Accumulator (A).** The accumulator is an 8-bit general purpose register used in all arithmetic calculations, logical operations, and data manipulations. The accumulator is addressed in the data space as RAM location at the FFh address.

Accordingly, the ST638x instruction set can use the accumulator as any other register of the data space.

Figure 5. ST638x Core Programming Model

Figure 4. ST6365,67,75,77,85,87 Core Block Diagram

# ST638x CORE (Continued)

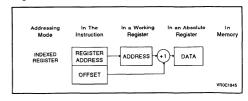

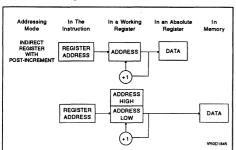

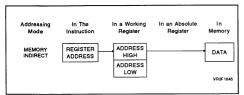

Indirect Registers (X, Y). These two indirect registers are used as pointers to the memory locations in the data space. They are used in the register-indirect addressing mode. These registers can be addressed in the data space as RAM locations at the 80h (X) and 81h (Y) addresses. They can also be accessed with the direct, short direct, or bit direct addressing modes. Accordingly, the ST638x instruction set can use the indirect registers as any other register of the data space.

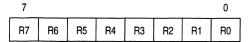

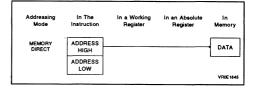

Short Direct Registers (V, W). These two registers are used to save one byte in short direct addressing mode. These registers can be addressed in the data space as RAM locations at the 82h (V) and 83h (W) addresses. They can also be accessed with the direct and bit direct addressing modes. Accordingly, the ST638x instruction set can use the short direct registers as any other register of the data space.

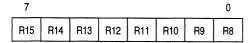

# Program Counter (PC)

The program counter is a 12-bit register that contains the address of the next ROM location to be processed by the core. This ROM location may be an opcode, an operand, or an address of operand. The 12-bit length allows the direct addressing of 4096 bytes in the program space. Nevertheless, if the program space contains more than 4096 locations, the further program space can be addressed by using the Program ROM Page Register. The PC value is incremented, after it is read for the address of the current instruction, by sending it through the ALU, so giving the address of the next byte in the program. To execute relative jumps the PC and the offset values are shifted through the ALU, where they will be added, and the result is shifted back into the PC. The program counter can be changed in the following ways:

# Flags (C, Z)

The ST638x Core includes three pairs of flags that correspond to 3 different modes: normal mode, interrupt mode and Non-Maskable-Interrupt-Mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during normal operation, one pair is used during the interrupt mode (CI,ZI) and one is used during the not-maskable interrupt mode (CNMI, ZNMI).

The ST638x Core uses the pair of flags that corresponds to the actual mode: as soon as an interrupt (resp. a Non-Maskable-Interrupt) is generated, the ST638x Core uses the interrupt flags (resp. the NMI flags) instead of the normal flags. When the RETI instruction is executed, the normal flags (resp. the interrupt flags) are restored if the MCU was in the normal mode (resp. in the interrupt mode) before the interrupt. Should be observed that each flag set can only be addressed in its own routine (Not-maskable interrupt, normal interrupt or main routine). The interrupt flags are not cleared during the context switching and so, they remain in the state they were at the exit of the last routine switching.

The Carry flag is set when a carry or a borrow occurs during arithmetic operations, otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction, and participates in the rotate left instruction.

The Zero flag is set if the result of the last arithmetic or logical operation was equal to zero, otherwise it is cleared.

The switching between these three sets is automatically performed when an NMI, an interrupt and a RETI instructions occur. As the NMI mode is automatically selected after the reset of the MCU, the ST638x Core uses at first the NMI flags.

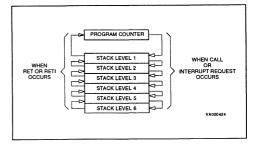

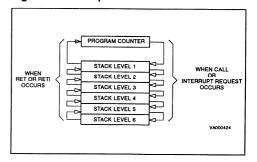

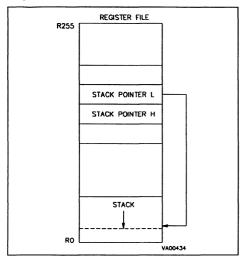

Figure 6. Stack Operation

# ST638x CORE (Continued)

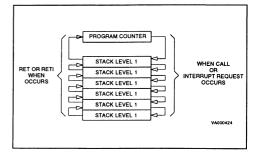

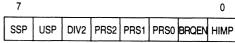

### Stack

The ST638x Core includes true LIFO hardware stack that eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level is shifted into the next level while the content of the PC is shifted into the first level (the value of the sixth level will be lost). When subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC and the value of each level is shifted back into the previous level. These two operating modes are described in Figure 6. Since the accumulator, as all other data space registers, is not stored in this stack the handling of this registers shall be performed inside the subroutine. The stack pointer will remain in its deepest position, if more than 6 calls or interrupts are executed, so that the last return address will be lost. It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

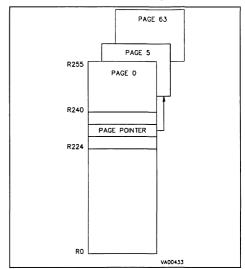

# **Memory Registers**

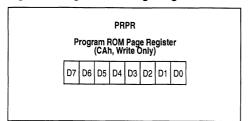

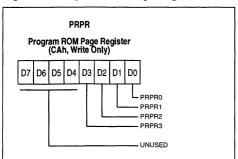

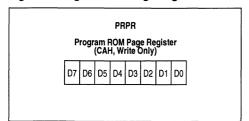

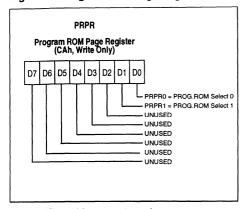

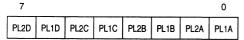

The PRPR can be addressed like a RAM location in the Data Space at the CAh address; nevertheless it is a write-only register that can not be accessed with single-bit operations. This register is used to select the 2-Kbyte ROM bank of the Program Space that will be addressed. The number of the page has to be loaded in the PRPR. The PRPR is not cleared during the MCU initialization and should therefore be defined before jumping out of the static page. Refer to the Program Space description for additional information concerning the use of this register. The PRPR is not modified when an interrupt or a subroutine occurs.

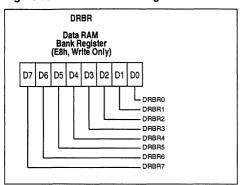

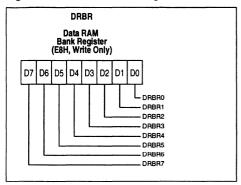

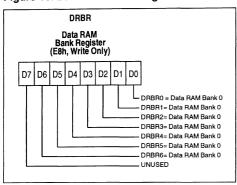

Figure 7. Program ROM Page Register

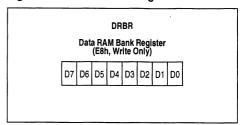

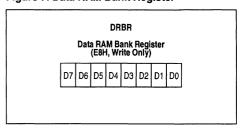

The DRBR can be addressed like a RAM location in the Data Space at the E8h address, nevertheless it is write-only register that can not be accessed with single-bit operations. This register is used to select the desired 64-byte RAM/EEPROM bank of the Data Space. The number of the bank has to be loaded in the DRBR and the instruction has to point to the selected location as it was in the 0 bank (from 00h address to 3Fh address). This register is undefined after Reset. Refer to the Data Space description for additional information. The DRBR register is not modified when a interrupt or a subroutine occurs.

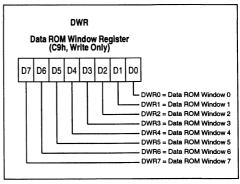

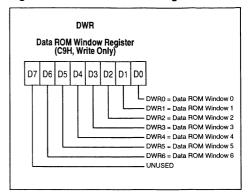

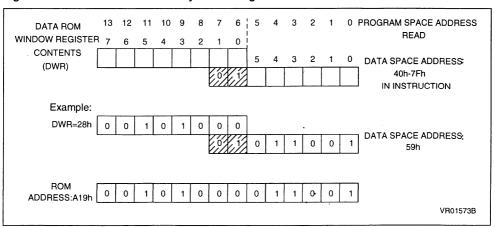

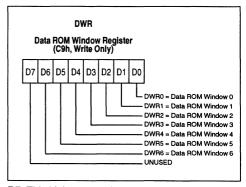

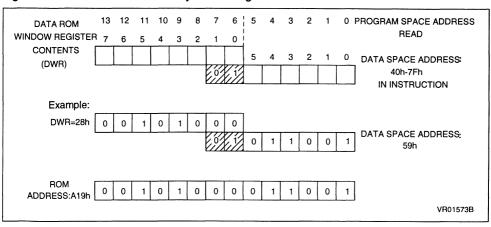

Figure 8. Data RAM Bank Register

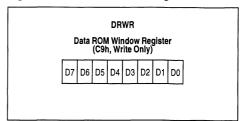

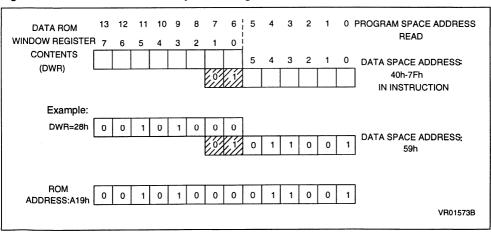

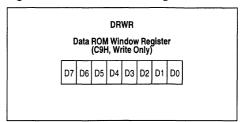

The DRWR register can be addressed like a RAM location in the Data Space at the C9h address, nevertheless it is write-only register that can not be accessed with single-bit operations. This register is used to move up and down the 64-byte read-only data window (from the 40h address to 7Fh address of the Data Space) along the ROM of the MCU by step of 64 bytes. The effective address of the byte to be read as a data in the ROM is obtained by the concatenation of the 6 less significant bits of the address given in the instruction (as less significant bits) and the content of the DRWR (as most significant bits). Refer to the Data Space description for additional information.

Figure 9. Data ROM Window Register

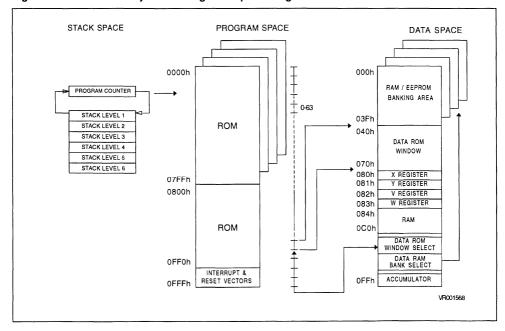

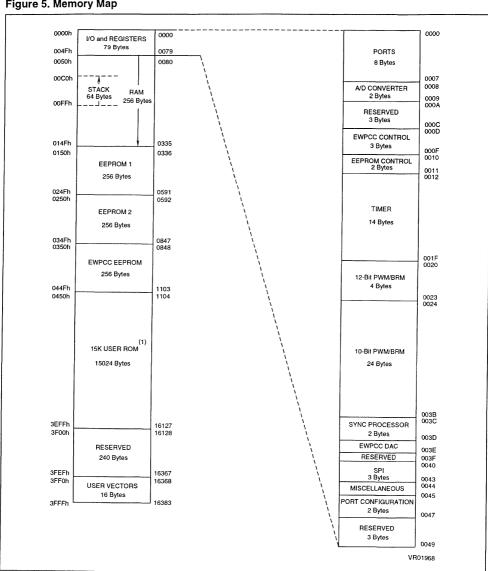

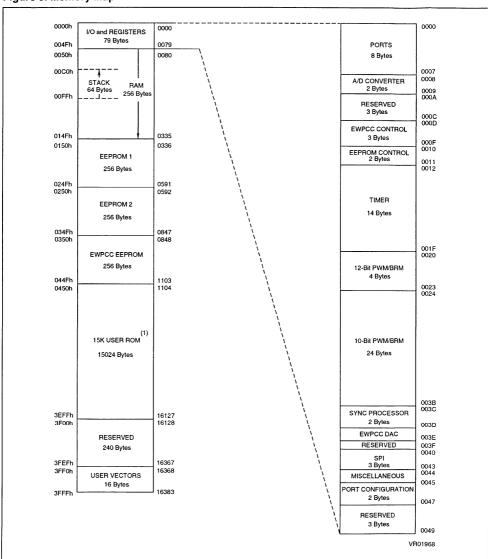

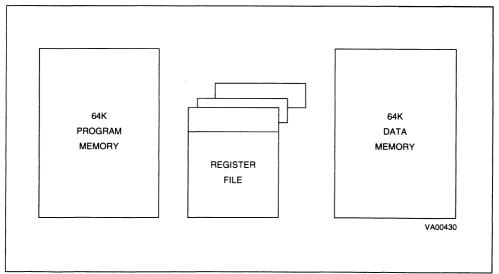

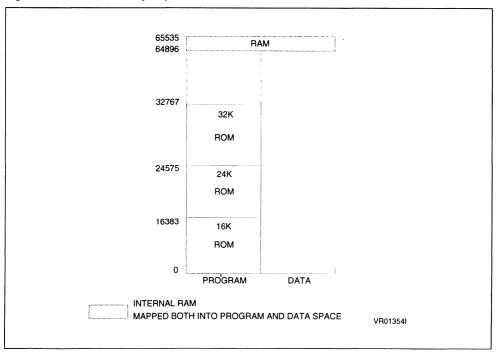

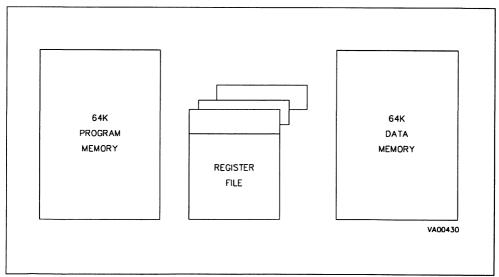

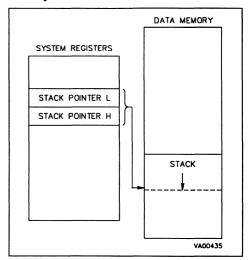

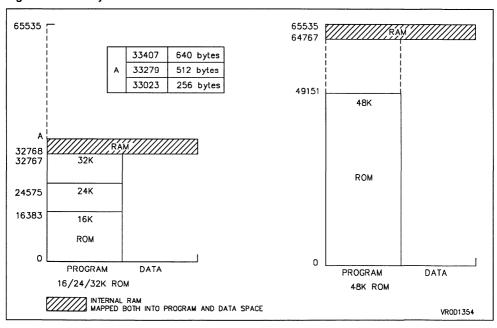

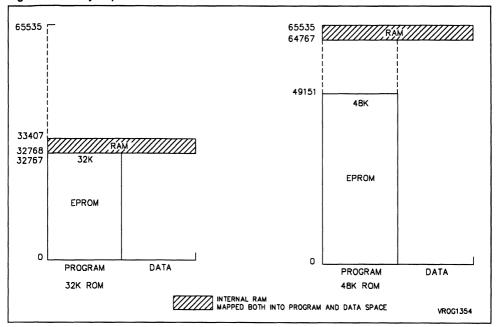

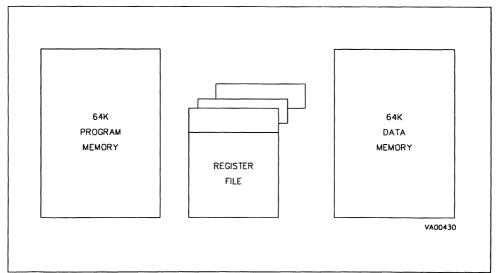

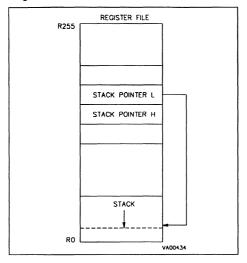

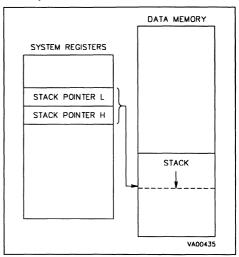

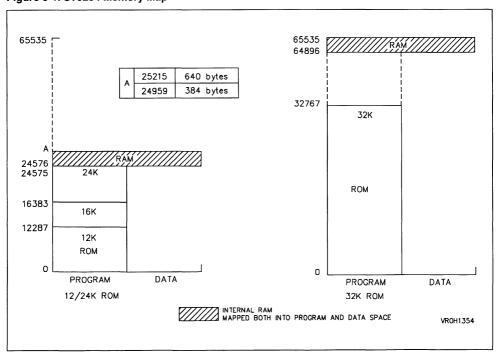

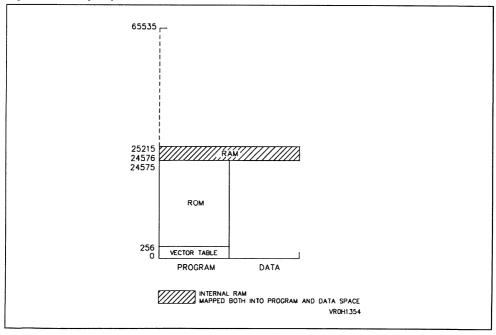

### MEMORY SPACES

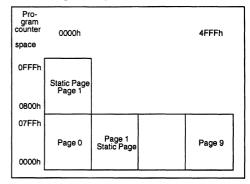

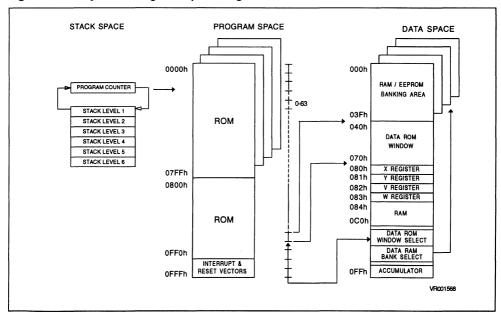

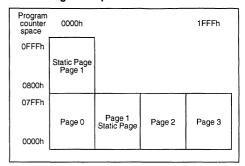

The MCUs operate in three different memory spaces: Stack Space, Program Space, and Data Space. (Figure 10 refers to the ST638x which has a total of 20K bytes of ROM).

## Stack Space

The stack space consists of six 12 bit registers that are used for stacking subroutine and interrupt return addresses plus the current program counter register.

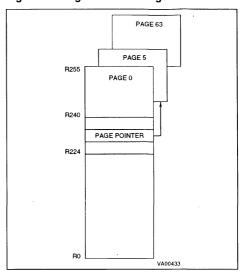

# **Program Space**

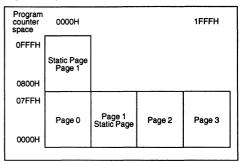

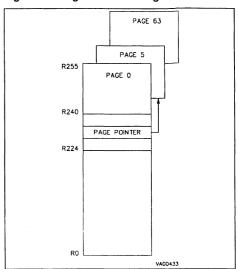

The program space is physically implemented in the ROM and includes all the instructions that are to be executed, as well as the data required for the immediate addressing mode instructions, the reserved test area and user vectors. It is addressed thanks to the 12-bit Program Counter register (PC register) and so, the ST638x Core can directly address up to 4K bytes of Program Space. Nevertheless, the Program Space can be extended by the addition of 2-Kbyte ROM banks as it is shown in Figure 12 in which a 20K bytes memory is described. These banks are addressed by pointing to the 000h-7FFh locations of the Program Space thanks to the Program Counter, and by writing the appropriate code in the Program ROM Page Register (PRPR) located at the CAh address of the Data Space, Because interrupts and common subroutines should be available all the time only the lower 2K byte of the 4K program space are bank switched while the upper 2K byte can be seen as static space. Table 3 gives the different codes that allows the selection of the corresponding banks. Note that, from the memory point of view, the Page 1 and the Static Page represent the same physical memory: it is only a different way of addressing the same location. On the ST6385 and ST6387, a total of 20480 bytes of ROM have been implemented; 20140 are available as user ROM while 340 are reserved for testing.

Figure 11. ST638x 20K Bytes Program Space Addressing Description

Figure 10. ST638x Memory Addressing Description Diagram

Figure 12. Program ROM Page Register

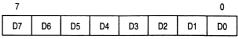

D7-D5. These bits are not used.

**PRPR4-PRPR0.** These are the program ROM banking bits and the value loaded selects the corresponding page to be addressed in the lower part of 4K program address space as specified in Table 3. This register is undefined on reset.

Note. The number of bits implemented depends on the size of the ROM of the device. Only the lower part of address space has been bankswitched because interrupt vectors and common subroutines should be available all the time. The reason of this structure is due to the fact that it is not possible to jump from a dynamic page to another, unless jumping back to the static page, changing contents of PRPR, and, than, jumping to a different dynamic page.

Care is required when handling the PRPR as it is write only. For this reason, it is not allowed to change the PRPR contents while executing interrupts drivers, as the driver cannot save and than restore its previous content. Anyway, this operation may be necessary if the sum of common routines and interrupt drivers will take more than 2K bytes; in this case could be necessary to divide the

interrupt driver in a (minor) part in the static page (start and end), and in the second (major) part in one dynamic page. If it is impossible to avoid the writing of this register in interrupts drivers, an image of this register must be saved in a RAM location, and each time the program writes the PRPR it writes also the image register. The image register must be written first, so if an interrupt occurs between the two instructions the PRPR is not affected.

Table 3. ST636x, 7x, 8x Program ROM Page Register Coding

| PRPR3 | PRPR2 | PRPR1 | PRPR0 | PC11 | Memory<br>Page             |

|-------|-------|-------|-------|------|----------------------------|

| x     | х     | X     | x     | 1    | Static<br>Page<br>(Page 1) |

| 0     | 0     | 0     | 0     | 0    | Page 0                     |

| 0     | 0     | 0     | 1     | 0    | Page 1<br>(Static<br>Page) |

| 0     | 0     | 1     | 0     | 0    | Page 2                     |

| 0     | 0     | 1     | 1     | 0    | Page 3                     |

| 0     | 1     | 0     | 0     | 0    | Page 4                     |

| 0     | 1     | 0     | 1     | 0    | Page 5                     |

| 0     | 1     | 1     | 0     | 0    | Page 6                     |

| 0     | 1     | 1     | 1     | 0    | Page 7                     |

| 1     | 0     | 0     | 0     | 0    | Page 8                     |

| 1     | 0     | 0     | 1     | 0    | Page 9                     |

# Table 4. ST638x Program ROM Map (up to 20K Bytes)

| ROM Page           | Device Address                                                                         | Description                                                          |

|--------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| PAGE 0             | 0000h-007Fh<br>0080h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 1<br>"STATIC" | 0800h-0F9Fh<br>0FA0h-0FEFh<br>0FF0h-0FF7h<br>0FF8h-0FFBh<br>0FFCh-0FFDh<br>0FFEh-0FFFh | User ROM Reserved Interrupt Vectors Reserved NMI Vector Reset Vector |

| PAGE 2             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 3             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM (End of 8k ST6365, 67)                          |

| PAGE 4             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 5             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 6             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM (End of 14k ST6375, 77)                         |

| PAGE 7             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 8             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 9             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM (End of 20k ST6385, 87)                         |

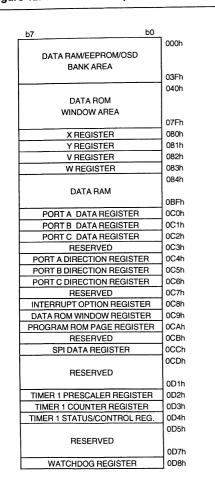

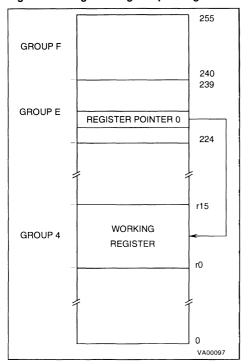

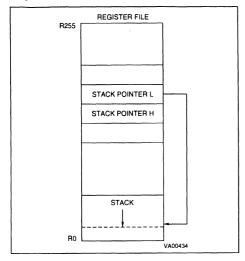

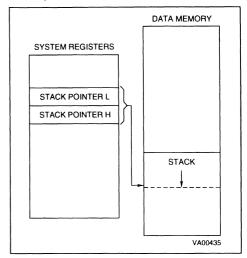

# **Data Space**

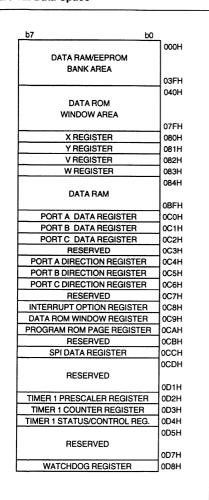

The instruction set of the ST638x Core operates on a specific space, named Data Space that contains all the data necessary for the processing of the program. The Data

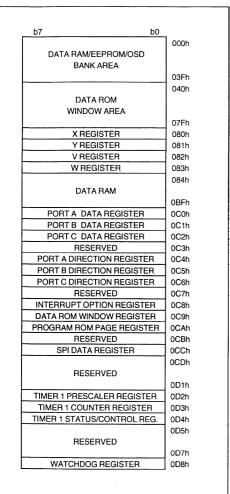

Figure 13. ST638x Data Space

Space allows the addressing of RAM (256 bytes for the ST638x family), EEPROM (384 bytes), ST638x Core/peripheral registers, and read-only data such as constants and the look-up tables.

Figure 14. ST638x Data Space (Continued)

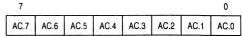

| b7 b0                         | 1    |

|-------------------------------|------|

| RESERVED                      | 0D9l |

| TIMER 2 PRESCALER REGISTER    | 0DAI |

| TIMER 2 COUNTER REGISTER      | ODB  |

| TIMER 2 STATUS CONTROL REG.   | 0DC  |

|                               | ODD: |

| RESERVED                      |      |

|                               | 0DF  |

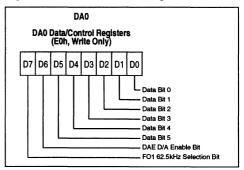

| DA0 DATA/CONTROL REGISTER     | 0E0  |

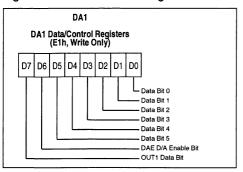

| DA1 DATA/CONTROL REGISTER     | 0E1  |

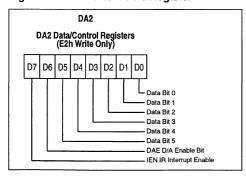

| DA2 DATA/CONTROL REGISTER     | 0E2  |

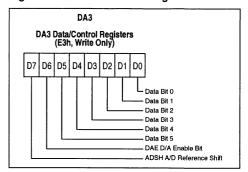

| DA3 DATA/CONTROL REGISTER     | 0E3l |

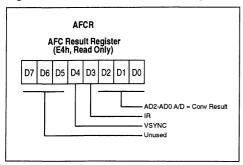

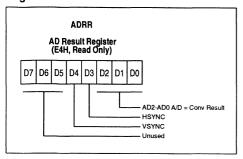

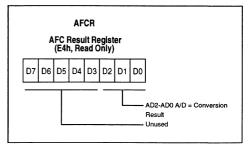

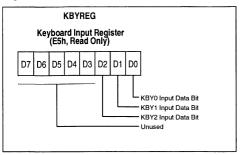

| AFC, IR & OSD RESULT REGISTER | 0E4l |

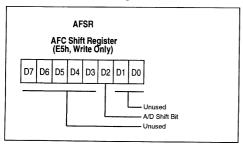

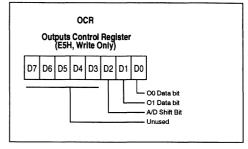

| OUTPUTS CONTROL REGISTER      | 0E5l |

| DA4 DATA/CONTROL REGISTER     | 0E6l |

| DA5 DATA/CONTROL REGISTER     | 0E71 |

| DATA RAM BANK REGISTER        | 0E8I |

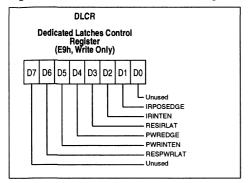

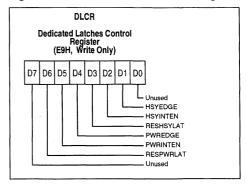

| DEDIC. LATCHES CONTROL REG.   | 0E9t |

| EEPROM CONTROL REGISTER       | 0EAI |

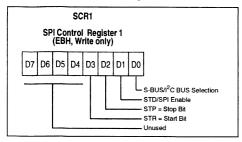

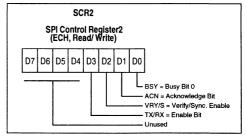

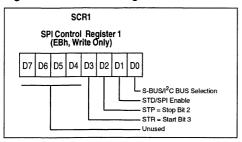

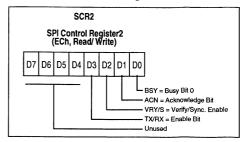

| SPI CONTROL REGISTER 1        | 0EBI |

| SPI CONTROL REGISTER 2        | 0ECI |

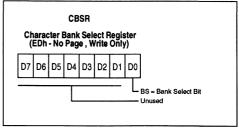

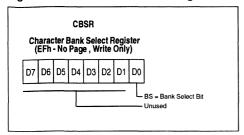

| OSD CHARAC. BANK SELECT REG.  | 0EDI |

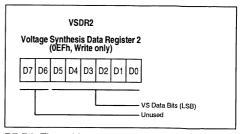

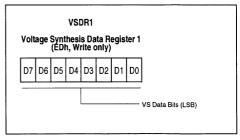

| VS DATA REGISTER 1            | 0EEI |

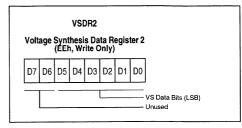

| VS DATA REGISTER 2            | 0EFI |

|                               | OFO  |

| RESERVED                      |      |

|                               | OFE  |

| ACCUMULATOR                   | OFF  |

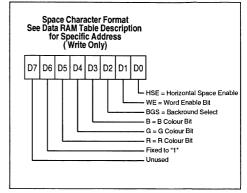

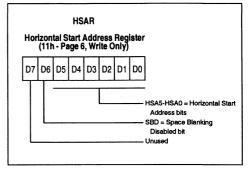

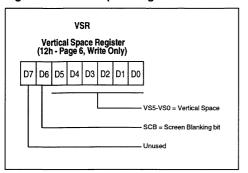

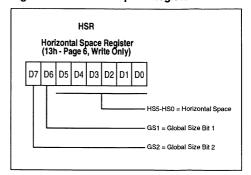

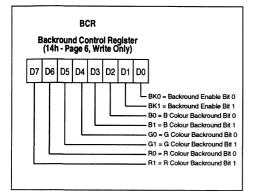

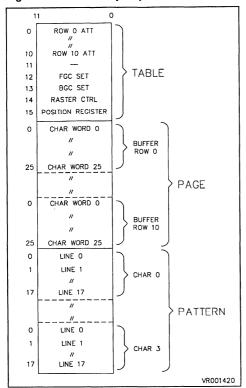

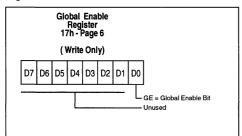

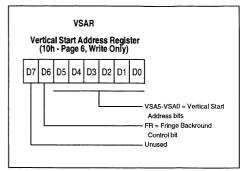

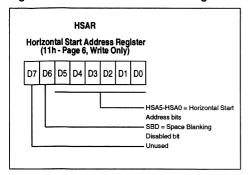

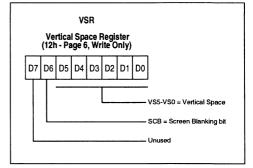

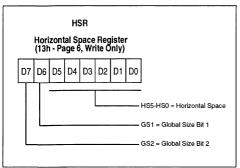

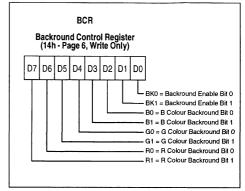

OSD CONTROL REGISTERS LO-

IN PAGE 6 OF BANKED DATA RAM

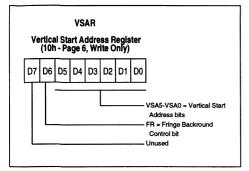

| VERTICAL START ADDRESS REG.   | 010h |

|-------------------------------|------|

| HORIZONTAL START ADDRESS REG. | 011h |

| VERTICAL SPACE REGISTER       | 012h |

| HORIZONTAL SPACE REGISTER     | 013h |

| BACKGROUND COLOUR REGISTER    | 014h |

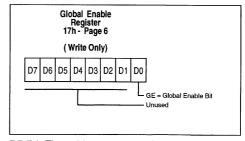

| GLOBAL ENABLE REGISTER        | 017h |

|                               |      |

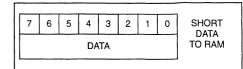

Data ROM Addressing. All the read-only data are physically implemented in the ROM in which the Program Space is also implemented. The ROM therefore contains the program to be executed and also the constants and the look-up tables needed for the program. The locations of Data Space in which the different constants and look-up tables are addressed by the ST638x Core can be considered as being a 64-byte window through which it is possible to access to the read-only data stored in the ROM. This window is located from the 40h address to the 7Fh address in the Data space and allows the direct reading of the bytes from the 000h address to the 03Fh address in the ROM. All the bytes of the ROM can be used to store either instructions or read-only data. Indeed, the window can be moved by step of 64 bytes along the ROM in writing the appropriate code in the Write-only Data ROM Window register (DRWR, location C9h). The effective address of the byte to be read as a data in the ROM is obtained by the concatenation of the 6 less significant bits of the address in the Data Space (as less significant bits) and the content of the DRWR (as most significant bits). So when addressing location 40h of data space, and 0 is loaded in the DRWR, the physical addressed location in ROM is 00h.

Note. The data ROM window cannot address windows above the 16k byte range.

Figure 15. Data ROM Window Register

**DWR7-DWR0.** These are the Data Rom Window bits that correspond to the upper bits of data ROM program space. This register is undefined after reset.

Note. Care is required when handling the DRWR as it is write only. For this reason, it is not allowed to change the DRWR contents while executing interrupts drivers, as the driver cannot save and than restore its previous content. If it is impossible to avoid the writing of this register in interrupts drivers, an image of this register must be saved in a RAM location, and each time the program writes the DRWR it writes also the image register. The image register must be written first, so if an interrupt occurs between the two instructions the DRWR register is not affected.

Figure 16. Data ROM Window Memory Addressing

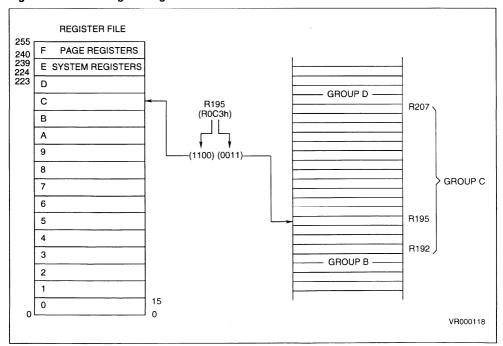

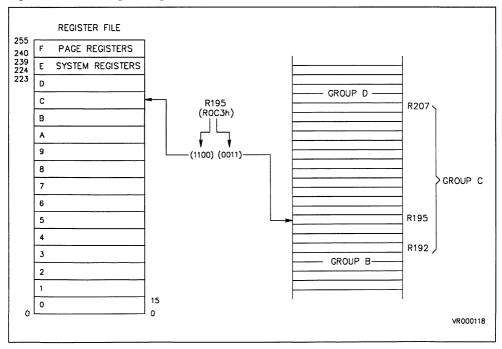

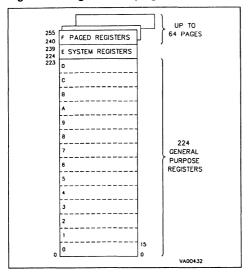

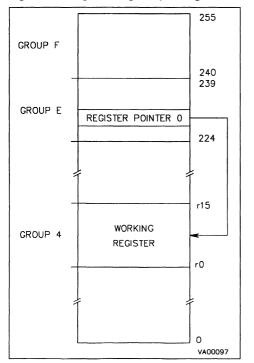

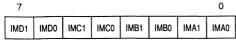

## Data RAM/EEPROM/OSD RAM Addressing

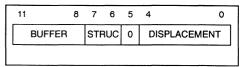

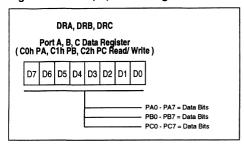

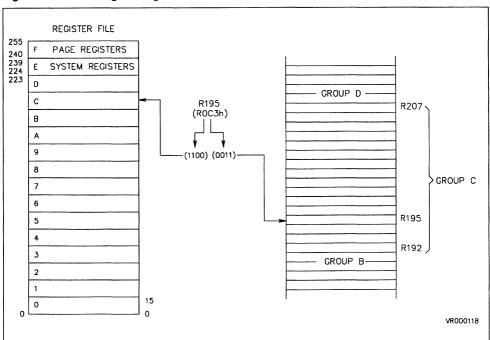

In all members of the ST638x family 64 bytes of data RAM are directly addressable in the data space from 80h to BFh addresses. The additional 192 bytes of RAM, the 384 bytes of EEPROM, and the OSD RAM can be addressed using the banks of 64 bytes located between addresses 00h and 3Fh. The selection of the bank is done by programming the Data RAM Bank Register (DRBR) located at the E8h address of the Data Space. In this way each bank of RAM, EEPROM or OSD RAM can select 64 bytes at a time. No more than one bank should be set at a time.

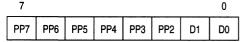

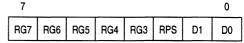

Figure 17. Data RAM Bank Register

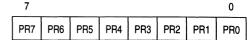

**DRBR7,DRBR1,DRBR0.** These bits select the EEPROM pages.

**DRBR6, DRBR5.** Each of these bits, when set, will select one OSD RAM register page.

**DRBR4,DRBR3,DRBR2.** Each of these bits, when set, will select one RAM page.

This register is undefined after reset.

Table 5 summarizes how to set the Data RAM Bank Register in order to select the various banks or pages.

### Note:

Care is required when handling the DRBR as it is write only. For this reason, it is not allowed to change the DRBR contents while executing interrupts drivers, as the driver cannot save and than restore its previous content. If it is impossible to avoid the writing of this register in interrupts drivers, an image of this register must be saved in a RAM location, and each time the program writes the DRBR it writes also the image register.

The image register must be written first, so if an interrupt occurs between the two instructions the DRBR is not affected.

Table 5. Data RAM Bank Register Set-up

|      | DRBR Value | Selection     |  |

|------|------------|---------------|--|

| Hex. | Binary     | Selection     |  |

| 01h  | 0000 0001  | EEPROM Page 0 |  |

| 02h  | 0000 0010  | EEPROM Page 1 |  |

| 03h  | 0000 0011  | EEPROM Page 2 |  |

| 81h  | 1000 0001  | EEPROM Page 3 |  |

| 82h  | 1000 0010  | EEPROM Page 4 |  |

| 83h  | 1000 0011  | EEPROM Page 5 |  |

| 04h  | 0000 0100  | RAM Page 2    |  |

| 08h  | 0000 1000  | RAM Page 3    |  |

| 10h  | 0001 0000  | RAM Page 4    |  |

| 20h  | 0010 0000  | OSD Page 5    |  |

| 40h  | 0100 0000  | OSD Page 6    |  |

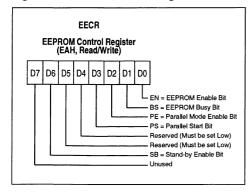

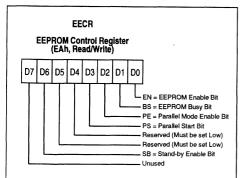

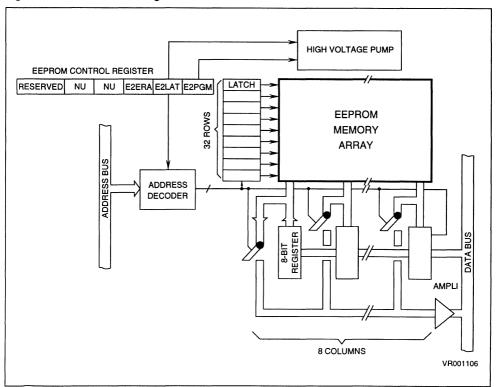

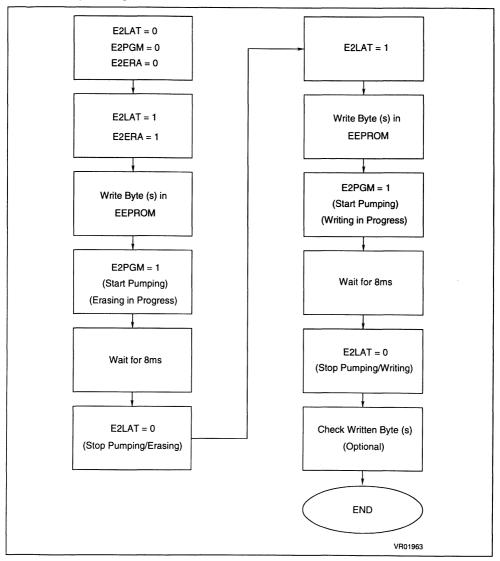

# **EEPROM Description**

The data space of ST638x family from 00h to 3Fh is paged as described in Table 5. 384 bytes of EEPROM located in six pages of 64 bytes (pages 0,1,2,3,4 and 5, see Table 5).

Through the programming of the Data RAM Bank Register (DRBR=E8h) the user can select the bank or page leaving unaffected the way to address the static registers. The way to address the "dynamic" page is to set the DRBR as described in Table 5 (e.g. to select EEPROM page 0, the DRBR has to be loaded with content 01h, see Data RAM/EEPROM/OSD RAM addressing for additional information). Bits 0, 1 and 7 of the DRBR are dedicated to the EEPROM.

The EEPROM pages do not require dedicated instructions to be accessed in reading or writing. The EEPROM is controlled by the EEPROM Control Register (EECR=EAh). Any EEPROM location can be read just like any other data location, also in terms of access time.

To write an EEPROM location takes an average time of 5 ms (10ms max) and during this time the EEPROM is not accessible by the Core. A busy flag can be read by the Core to know the EEPROM status before trying any access. In writing the EEPROM can work in two modes: Byte Mode (BMODE) and Parallel Mode (PMODE). The BMODE is the normal way to use the EEPROM and consists in accessing one byte at a time. The PMODE consists in accessing 8 bytes per time.

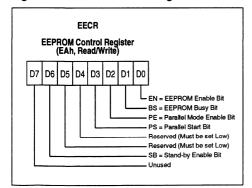

Figure 18. EEPROM Control Register

## D7. Not used

**SB.** WRITE ONLY. If this bit is set the EEPROM is disabled (any access will be meaningless) and the power consumption of the EEPROM is reduced to the leakage values.

**D5, D4.** Reserved for testing purposes, they must be set to zero.

PS. SET ONLY. Once in Parallel Mode, as soon as the user software sets the PS bit the parallel writing of the 8 adjacent registers will start. PS is internally reset at the end of the programming procedure. Note that less than 8 bytes can be written; after parallel programming the remaining undefined bytes will have no particular content.

PE. WRITE ONLY. This bit must be set by the user program in order to perform parallel programming (more bytes per time). If PE is set and the "parallel start bit" (PS) is low, up to 8 adjacent bytes can be written at the maximum speed, the content being stored in volatile registers. These 8 adjacent bytes can be considered as row, whose A7, A6, A5, A4, A3 are fixed while A2, A1 and A0 are the changing bytes. PE is automatically reset at the end of any parallel programming procedure. PE can be reset by the user software before starting the programming procedure, leaving unchanged the EEPROM registers.

BS. READ ONLY. This bit will be automatically set by the CORE when the user program modifies an EEPROM register. The user program has to test it before any read or write EEPROM operation; any attempt to access the EEPROM while "busy bit" is set will be aborted and the writing procedure in progress completed.

**EN.** WRITE ONLY. This bit MUST be set to one in order to write any EEPROM register. If the user program will attempt to write the EEPROM when EN= "0" the involved registers will be unaffected and the "busy bit" will not be set.

After RESET the content of EECR register will be 00h.

### Notes:

When the EEPROM is busy (BS="1") the EECR can not be accessed in write mode, it is only possible to read BS status. This implies that as long as the EEPROM is busy it is not possible to change the status of the EEPROM control register. EECR bits 4 and 5 are reserved for test purposes, and must never be set to "1".

Additional Notes on Parallel Mode. If the user wants to perform a parallel programming the first action should be the set to one the PE bit; from this moment the first time the EEPROM will be addressed in writing, the ROW address will be latched and it will be possible to change it only at the end of the programming procedure or by resetting PE without programming the EEPROM. After the ROW address latching the Core can "see" just one EEPROM row (the selected one) and any attempt to write or read other rows will produce errors. Do not read the EEPROM while PE is set.

As soon as PE bit is set, the 8 volatile ROW latches are cleared. From this moment the user can load data in the whole ROW or just in a subset. PS setting will modify the EEPROM registers corresponding to the ROW latches accessed after PE. For example, if the software sets PE and accesses EEPROM in writing at addresses 18h,1Ah,1Bh and then sets PS, these three registers will be modified at the same time; the remaining bytes will have no particular content. Note that PE is internally reset at the end of the programming procedure. This implies that the user must set PE bit between two parallel programming procedures. Anyway the user can set and then reset PE without performing any EEPROM programming. PS is a set only bit and is internally reset at the end of the programming procedure. Note that if the user tries to set PS while PE is not set there will not be any programming procedure and the PS bit will be unaffected. Consequently PS bit can not be set if EN is low. PS can be affected by the user set if. and only if, EN and PE bits are also set to one.

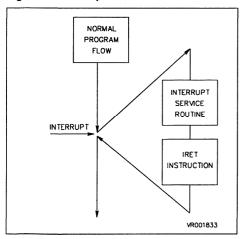

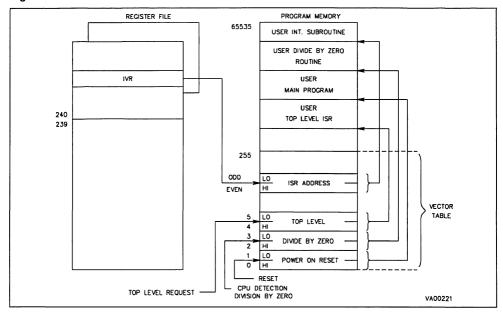

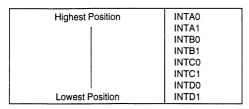

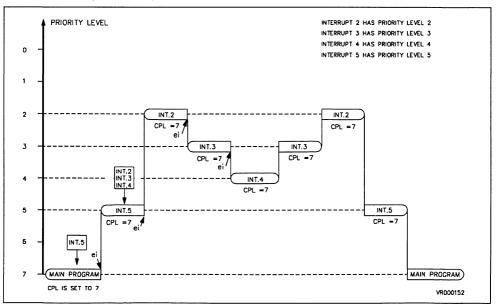

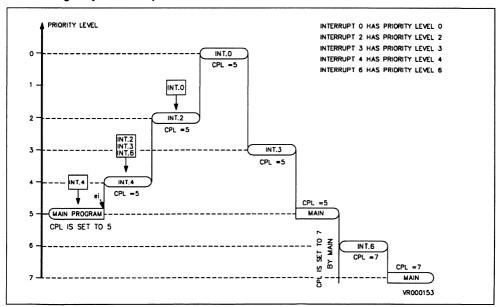

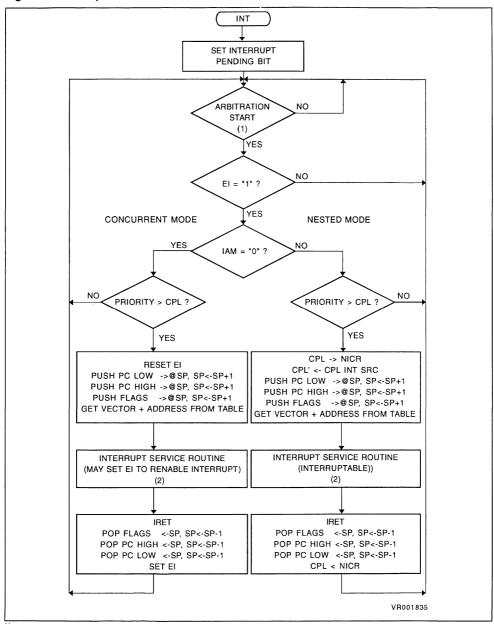

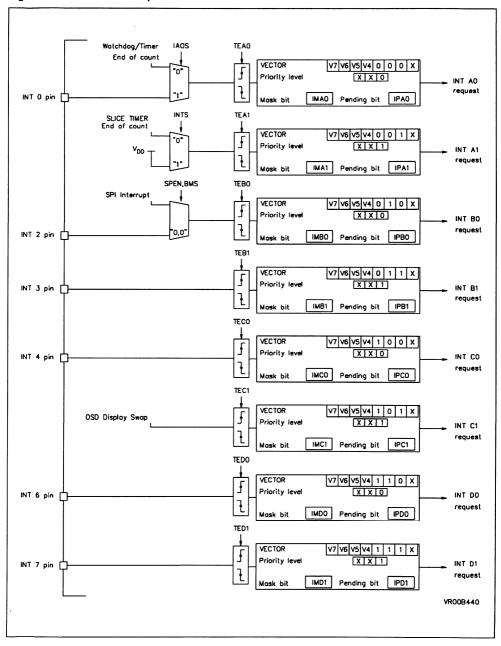

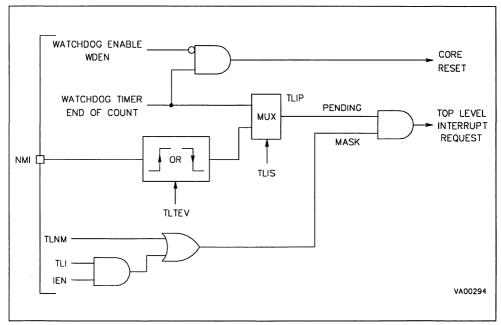

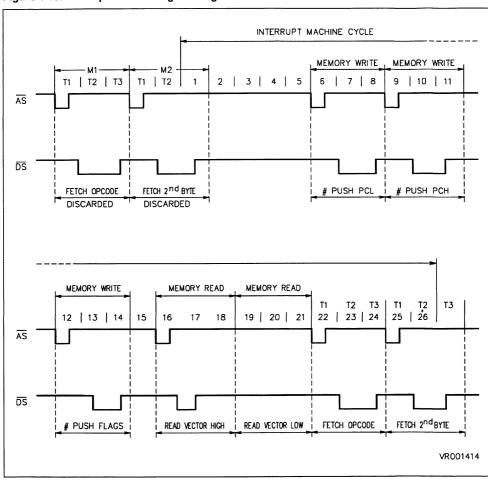

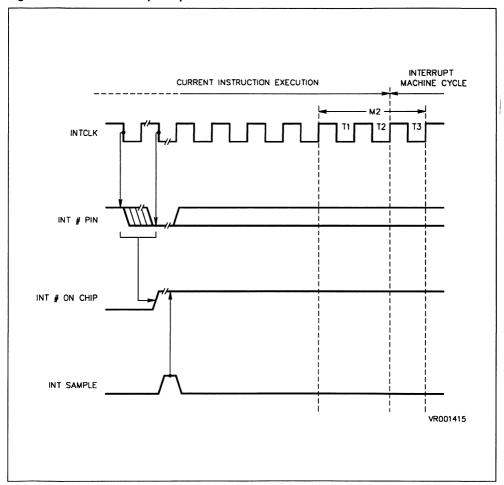

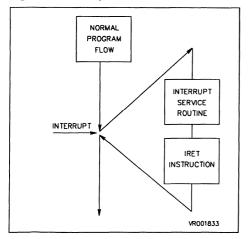

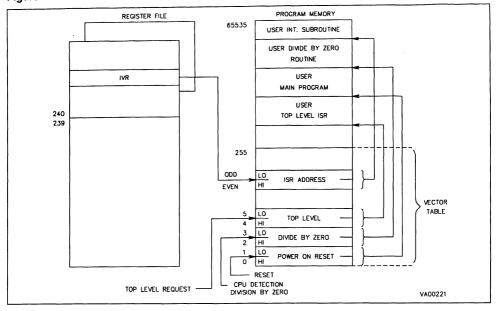

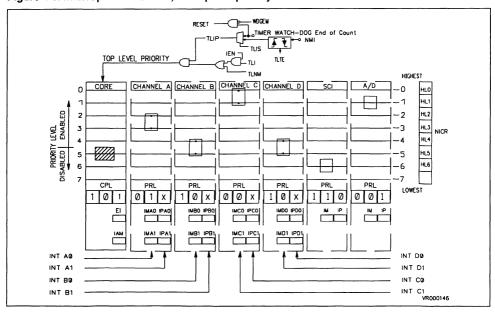

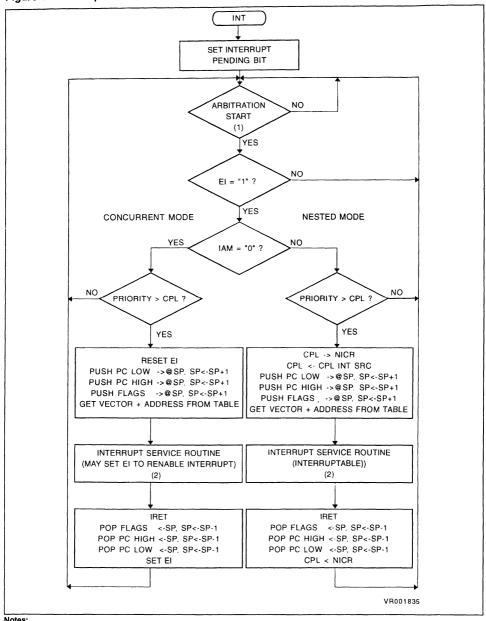

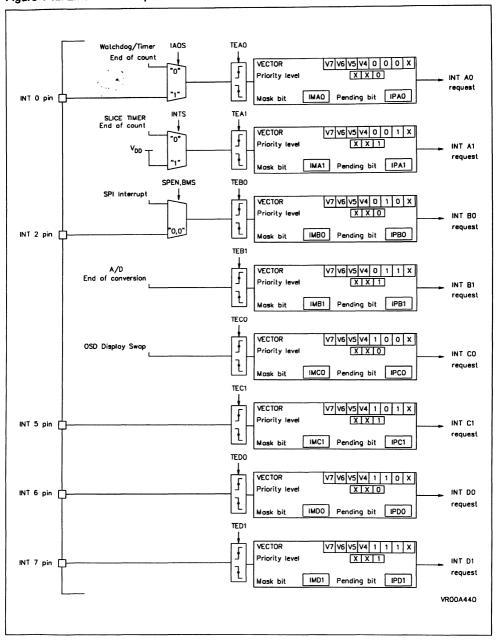

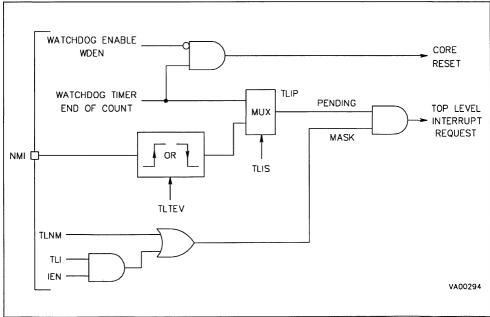

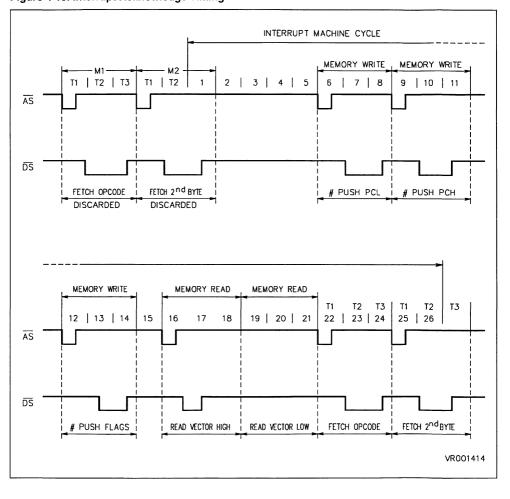

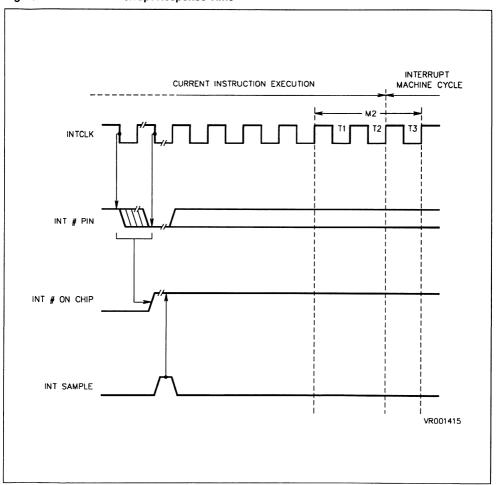

### INTERRUPT

The ST638x Core can manage 4 different maskable interrupt sources, plus one non-maskable interrupt source (top priority level interrupt). Each source is associated with a particular interrupt vector that contains a Jump instruction to the related interrupt service routine. Each vector is located in the Program Space at a particular address (see Table 6). When a source provides an interrupt request, and the request processing is also enabled by the ST638x Core, then the PC register is loaded with the address of the interrupt vector (i.e. of the Jump instruction). Finally, the PC is loaded with the address of the Jump instruction and the interrupt routine is processed.

The relationship between vector and source and the associated priority is hardware fixed for the different ST638x devices. For some interrupt sources it is also possible to select by software the kind of event that will generate the interrupt.

All interrupts can be disabled by writing to the GEN bit (global interrupt enable) of the interrupt option register (address C8h). After a reset, ST638x is in non maskable interrupt mode, so no interrupts will be accepted and NMI flags will be used, until RETI instruction is executed. If an interrupt is executed, one special cycle is made by the core, during that the PC is set to the related interrupt vector address. A jump instruction at this address has to redirect program execution to the beginning of the related interrupt routine. The interrupt detecting cycle, also resets the related interrupt flag (not available to the user), so that another interrupt can be stored for this current vector, while its driver is under execution.

If additional interrupts arrive from the same source, they will be lost. NMI can interrupt other interrupt routines at any time, while other interrupts cannot interrupt each other. If more than one interrupt is waiting for service, they are executed according to their priority. The lower the number, the higher the priority. Priority is, therefore, fixed. Interrupts are checked during the last cycle of an instruction (RETI included). Level sensitive interrupts have to be valid during this period.

# **INTERRUPT** (Continued)

# Table 6. Interrupt Vectors/Sources Relationships

| Interrupt Source    | Associated<br>Vector          | Vector Address |

|---------------------|-------------------------------|----------------|

| PC6/IRIN<br>Pin (1) | Interrupt<br>Vector # 0 (NMI) | 0FFCh-0FFDh    |

| Timer 2             | Interrupt<br>Vector # 1       | 0FF6h-0FF7h    |

| Vsync               | Interrupt<br>Vector # 2       | 0FF4h-0FF5h    |

| Timer 1             | Interrupt<br>Vector # 3       | 0FF2h-0FF3h    |

| PC4/PWRIN           | Interrupt<br>Vector # 4       | 0FF0h-0FF1h    |

Note: 1. This pin is associated with the NMI Interrupt Vector

# Interrupt Vectors/Sources

The ST638x Core includes 5 different interrupt vectors in order to branch to 5 different interrupt routines. The interrupt vectors are located in the fixed (or static) page of the Program Space.

The interrupt vector associated with the non-maskable interrupt source is named interrupt vector #0. It is located at the (FFCh,FFDh) addresses in the Program Space. This vector is associated with the PC6/:AIN pin.

The interrupt vectors located at addresses (FF6h,FF7h), (FF4h,FF5h), (FF2h,FF3h), (FF0h,FF1h) are named interrupt vectors #1, #2, #3 and #4 respectively. These vectors are associated with TIMER 2 (#1), VSYNC (#2), TIMER 1 (#3) and PC4(PWRIN) (#4).

# Interrupt Priority

The non-maskable interrupt request has the highest priority and can interrupt any other interrupt routines at any time, nevertheless the other interrupts cannot interrupt each other. If more than one interrupt request is pending, they are processed by the ST638x Core according to their priority level: vector #1 has the higher priority while vector #4 the lower. The priority of each interrupt source is hardware fixed.

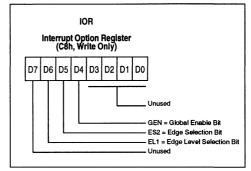

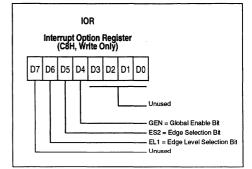

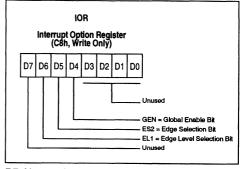

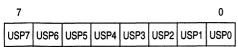

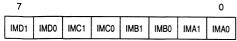

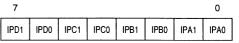

# **Interrupt Option Register**

The Interrupt Option Register (IOR register, location C8h) is used to enable/disable the individual interrupt sources and to select the operating mode of the external interrupt inputs. This register can be addressed in the Data Space as RAM location at the C8h address, nevertheless it is write-only register that can not be accessed with single-bit operations. The operating modes of the external interrupt inputs associated to interrupt vectors #1 and #2 are selected through bits 5 and 6 of the IOR register.

Figure 19. Interrupt Option Register

## D7. Not used.

**EL1.** This is the Edge/Level selection bit of interrupt #1. When set to one, the interrupt is generated on low level of the related signal; when cleared to zero, the interrupt is generated on falling edge. The bit is cleared to zero after reset.

**ES2.** This is the edge selection bit on interrupt #2. This bit is used on the ST638x devices with on-chip OSD generator for VSYNC detection.

**GEN.** This is the global enable bit. When set to one all interrupts are globally enabled; when this bit is cleared to zero all interrupts are disabled (excluding NMI).

D3 - D0. These bits are not used.

# **INTERRUPT** (Continued)

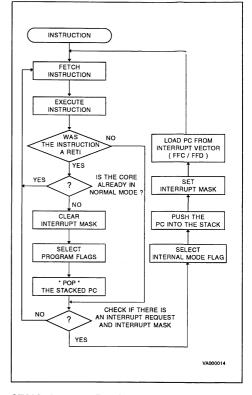

## Interrupt Procedure

The interrupt procedure is very similar to a call procedure; the user can consider the interrupt as an asynchronous call procedure. As this is an asynchronous event the user does not know about the context and the time at which it occurred. As a result the user should save all the data space registers which will be used inside the interrupt routines. There are separate sets of processor flags for normal, interrupt and non-maskable interrupt modes which are automatically switched and so these do not need to be saved.

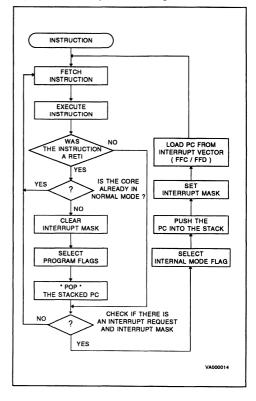

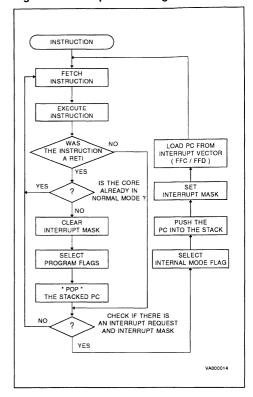

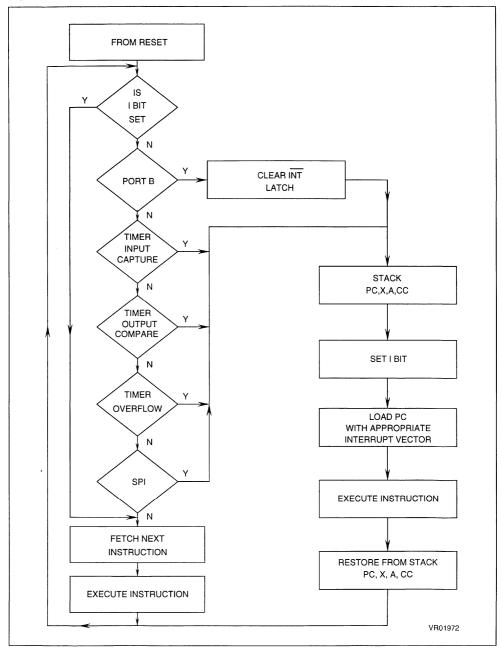

The following list summarizes the interrupt procedure (refer also to Figure 20. Interrupt Processing Flow Chart):

- Interrupt detection

- The flags C and Z of the main routine are exchanged with the flags C and Z of the interrupt routine (resp. the NMI flags)

- The value of the PC is stored in the first level of the stack - The normal interrupt lines are inhibited (NMI still active)

- The edge flip-flop is reset

- The related interrupt vector is loaded in the PC.

- User selected registers are saved inside the interrupt service routine (normally on a software stack)

- The source of the interrupt is found by polling (if more than one source is associated to the same vector)

- Interrupt servicing

- Return from interrupt (RETI)

- Automatically the ST638x core switches back to the normal flags (resp the interrupt flags) and pops the previous PC value from the stack

The interrupt routine begins usually by the identification of the device that has generated the interrupt request. The user should save the registers which are used inside the interrupt routine (that holds relevant data) into a software stack.

After the RETI instruction execution, the Core carries out the previous actions and the main routine can continue.

Figure 20. Interrupt Processing Flow-Chart

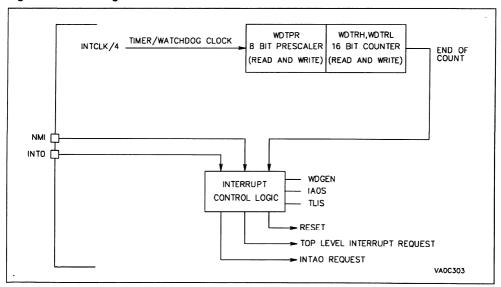

# ST638x Interrupt Details

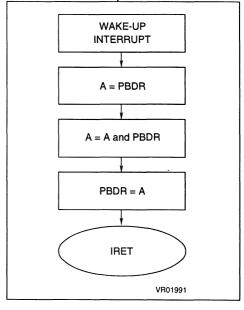

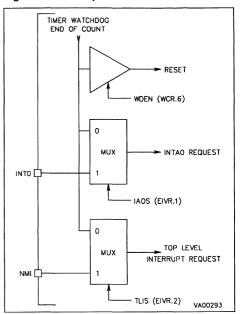

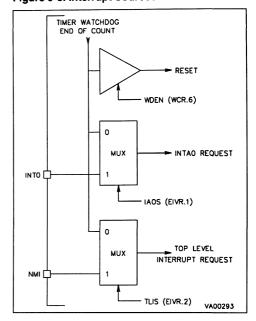

IR Interrupt (#0). The IRIN/PC6 Interrupt is connected to the first interrupt #0 (NMI, OFFCh). If the IRINT interrupt is disabled at the Latch circuitry, then it will be high. The #0 interrupt input detects a high to low level. Note that once #0 has been latched, then the only way to remove the latched #0 signal is to service the interrupt. #0 can interrupt the other interrupts. A simple latch is provided from the PC6(IRIN) pin in order to generate the IRINT signal. This latch can be triggered by either the positive or negative edge of IRIN signal. IRINT is inverted with respect to the latch. The latch can be read by software and reset by software.

# INTERRUPT (Continued)

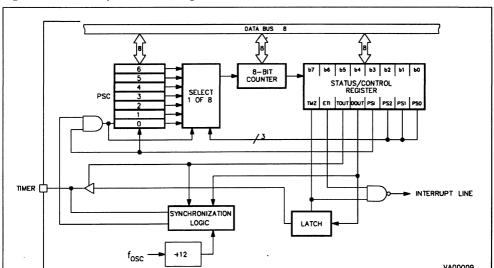

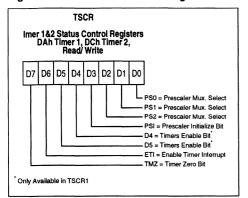

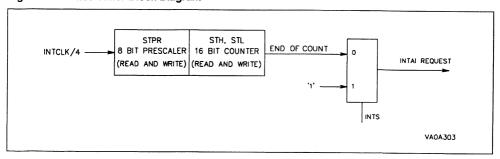

TIMER 2 Interrupt (#1). The TIMER 2 Interrupt is connected to the interrupt #1 (0FF6h). The TIMER 2 interrupt generates a low level (which is latched in the timer). Only the low level selection for #1 can be used. Bit 6 of the interrupt option register C8h has to be set.

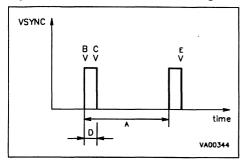

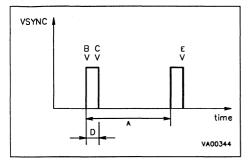

VSYNC Interrupt (#2). The VSYNC Interrupt is connected to the interrupt #2. When disabled the VSYNC INT signal is low. The VSYNC INT signal is inverted with respect to the signal applied to the VSYNC pin. Bit 5 of the interrupt option register C8h is used to select the negative edge (ES2=0) or the positive edge (ES2=1); the edge will depend on the application. Note that once an edge has been latched, then the only way to remove the latched signal is to service the interrupt. Care must be taken not to generate spurious interrupts. This interrupt may be used for synchronize to the VSYNC signal in order to change characters in the OSD only when the screen is on vertical blanking (if desired). This method may also be used to blink characters.

**TIMER 1 Interrupt (#3).** The TIMER 1 Interrupt is connected to the fourth interrupt #3 (0FF2h) which detects a low level (latched in the timer).

PWR Interrupt (#4). The PWR Interrupt is connected to the fifth interrupt #4 (0FF0h). If the PWRINT is disabled at the PWR circuitry, then it will be high. The #4 interrupt input detects a low level. A simple latch is provided from the PC4 (PWRIN)pin in order to generate the PWRINT signal. This latch can be triggered by either the positive or negative edge of the PWRIN signal. PWRINT is inverted with respect to the latch. The latch can be reset by software.

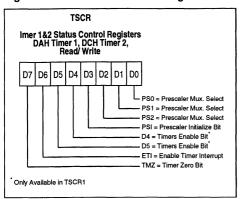

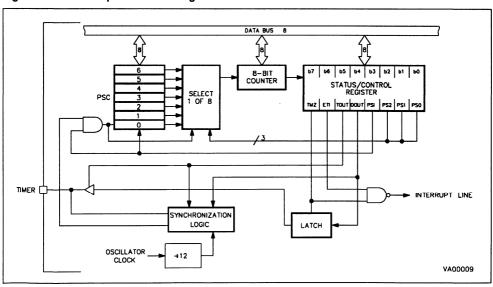

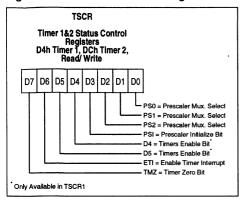

Notes Global disable does not reset edge sensitive interrupt flags. These edge sensitive interrupts become pending again when global disabling is released. Moreover, edge sensitive interrupts are stored in the related flags also when interrupts are globally disabled, unless each edge sensitive interrupt is also individually disabled before the interrupting event happens. Global disable is done by clearing the GEN bit of Interrupt option register, while any individual disable is done in the control register of the peripheral. The on-chip Timer peripherals have an interrupt request flag bit (TMZ), this bit is set to one when the device wants to generate an interrupt request and a mask bit (ETI) that must be set to one to allow the transfer of the flag bit to the Core.

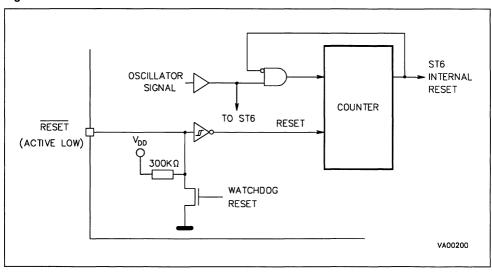

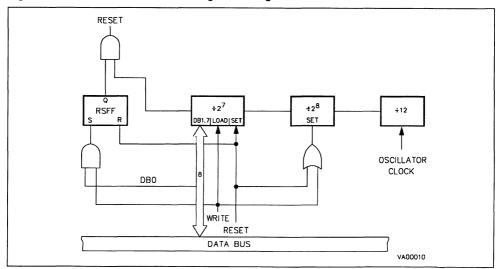

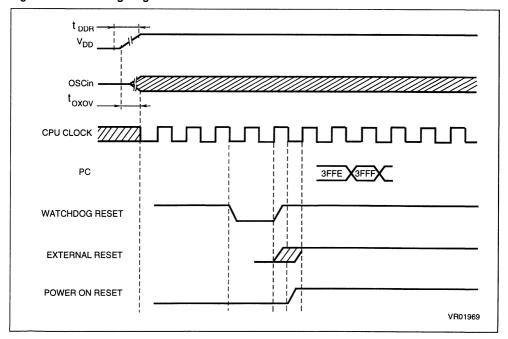

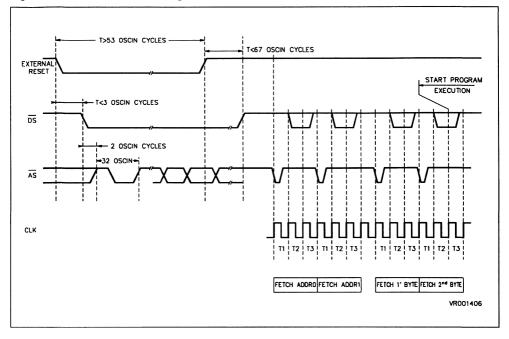

### RESET

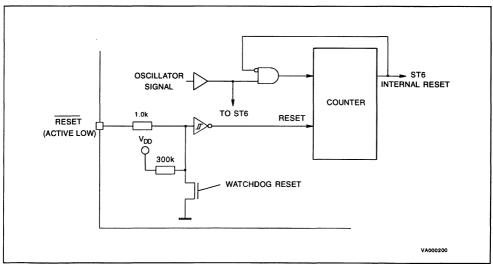

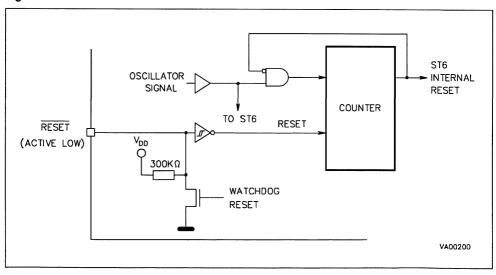

The ST638x devices can be reset in two ways: by the external reset input (RESET) tied low and by the hardware activated digital watchdog peripheral.

# **RESET Input**

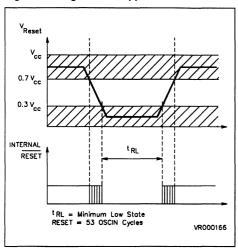

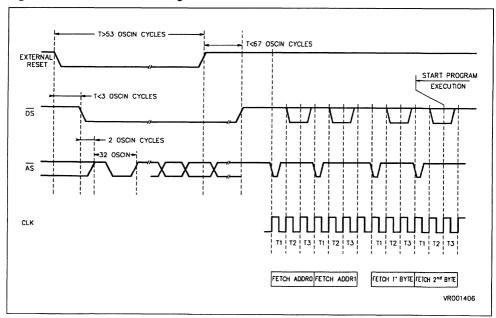

The external active low reset pin is used to reset the ST638x devices and provide an orderly software startup procedure. The activation of the Reset pin may occur at any time in the RUN or WAIT mode. Even short pulses at the reset pin will be accepted since the reset signal is latched internally and is only cleared after 2048 clocks at the oscillator pin. The clocks from the oscillator pin to the reset circuitry are buffered by a schmitt trigger so that an oscillator in start-up conditions will not give spurious clocks. When the reset pin is held low, the external crystal oscillator is also disabled in order to reduce current consumption. The MCU is configured in the Reset mode as long as the signal of the RESET pin is low. The processing of the program is stopped and the standard Input/Output ports (port A, port B and port C) are in the input state. As soon as the level on the reset pin becomes high, the initialization sequence is executed. Refer to the MCU initialization sequence for additional information.

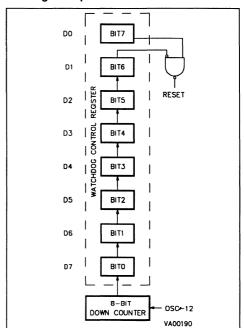

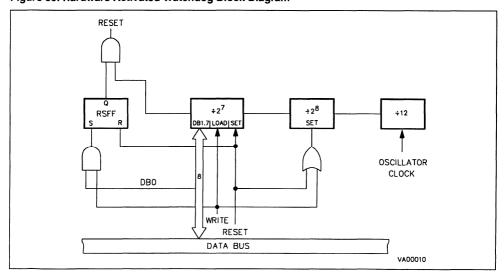

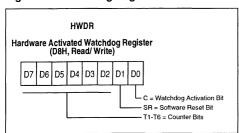

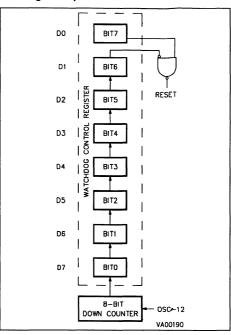

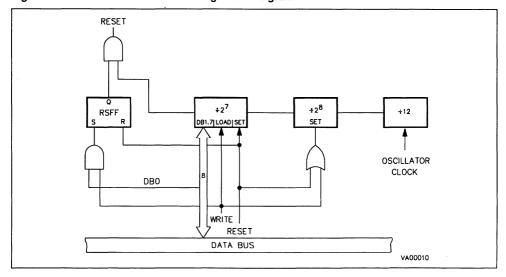

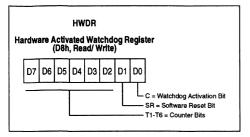

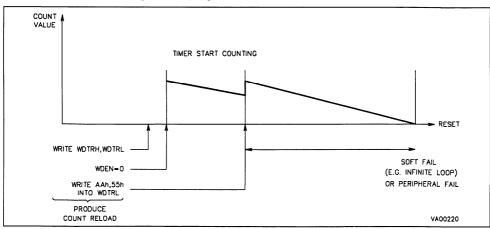

# **Watchdog Reset**

The ST638x devices are provided with an on-chip hardware activated digital watchdog function in order to provide a graceful recovery from a software upset. If the watchdog register is not refreshed and the end-of-count is reached, then the reset state will be latched into the MCU and an internal circuit pulls down the reset pin. This also resets the watchdog which subsequently turns off the pull-down and activates the pull-up device at the reset pin. This causes the positive transition at the reset pin. The MCU will then exit the reset state after 2048 clocks on the oscillator pin.

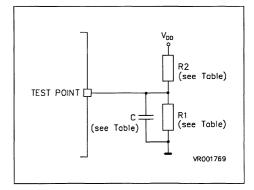

# **Application Notes**

An external resistor between  $V_{DD}$  and the reset pin is not required because an internal pull-up device is provided. The user may prefer to add an external pull-up resistor.

An internal Power-on device does not guarantee that the MCU will exit the reset state when  $V_{DD}$  is above 4.5V and therefore the RESET pin should be externally controlled.

Figure 21. Internal Reset Circuit

# **RESET** (Continued)

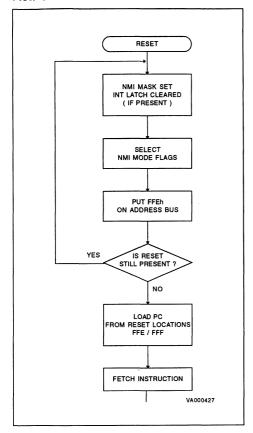

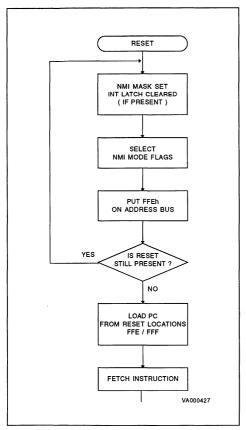

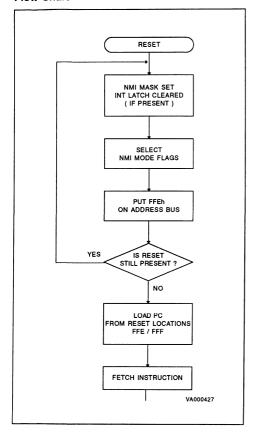

# Figure 22. Reset & Interrupt Processing Flow-Chart

Figure 23. Restart Initialization Program Flow-Chart

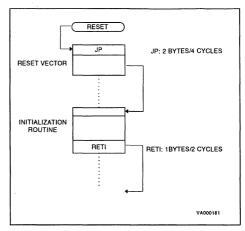

# **MCU Initialization Sequence**

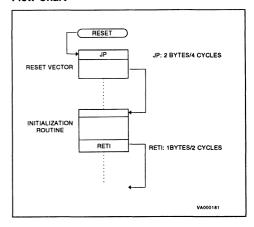

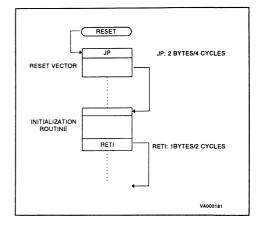

When a reset occurs the stack is reset to program counter, the PC is loaded with the address of the reset vector (located in the program ROM at addresses FFEh & FFFh). A jump instruction to the beginning of the program has to be written into these locations. After a reset the interrupt mask is automatically activated so that the Core is in non-maskable interrupt mode to prevent false or ghost interrupts during the restart phase. Therefore the restart routine should be terminated by a RETI instruction to switch to normal mode and enable interrupts. If no pending interrupt is present at the end of the reset routine, the ST638x will continue with the instruction after the RETI; otherwise the pending interrupt will be serviced.

## **RESET Low Power Mode**

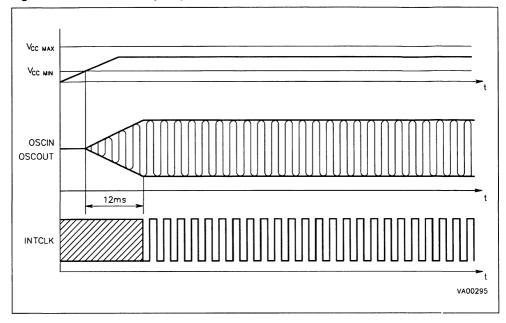

When the reset pin is low, the quartz oscillator is Disabled allowing reduced current consumption. When the reset pin is raised the quartz oscillator is enabled and oscillations will start to build up. The internal reset circuitry will count 2048 clocks on the oscillator pin before allowing the MCU to go out of the reset state; the clocks are after a Schmitt trigger so that false or multiple counts are not possible.

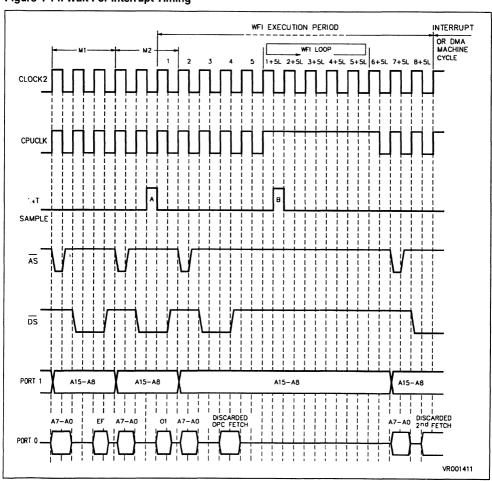

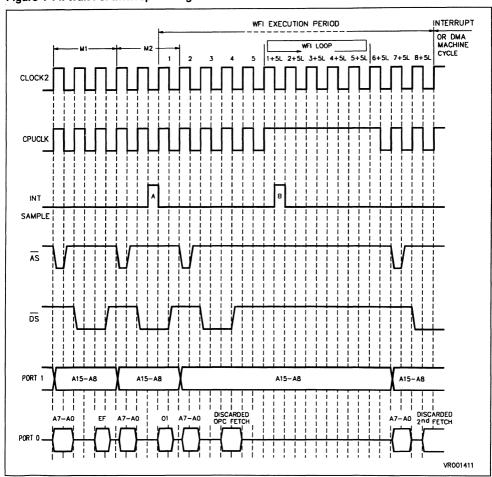

## **WAIT & STOP MODES**

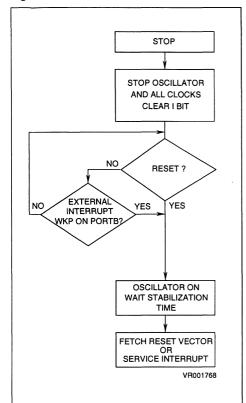

The STOP and WAIT modes have been implemented in the ST638x Core in order to reduce the consumption of the device when the latter has no instruction to execute. These two modes are described in the following paragraphs. On ST638x as the hardware activated digital watchdog function is present the STOP instruction is de-activated and any attempt to execute it will cause the automatic execution of a WAIT instruction.

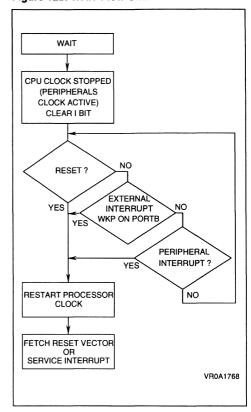

### **WAIT Mode**

The configuration of the MCU in the WAIT mode occurs as soon as the WAIT instruction is executed. The microcontroller can also be considered as being in a "software frozen" state where the Core stops processing the instructions of the routine, the contents of the RAM locations and peripheral registers are saved as long as the power supply voltage is higher than the RAM retention voltage but where the peripherals are still working.

The WAIT mode is used when the user wants to reduce the consumption of the MCU when it is in idle. while not losing count of time or monitoring of external events. The oscillator is not stopped in order to provide clock signal to the peripherals. The timers counting may be enabled (writing the PSI bit in TSCR register) and the timer interrupt may be also enabled before entering the WAIT mode; this allows the WAIT mode to be left when timer interrupt occurs. If the exit from the WAIT mode is performed with a general RESET (either from the activation of the external pin or by watchdog reset) the MCU will enter a normal reset procedure as described in the RESET chapter. If an interrupt is generated during WAIT mode the MCU behaviour depends on the state of the ST638x Core before the initialization of the WAIT sequence, but also of the kind of the interrupt request that is generated. This case will be described in the following paragraphs. In any case, the ST638x Core does not generate any delay after the occurrence of the interrupt because the oscillator clock is still available.

# STOP Mode

On ST638x the hardware watchdog is present and the STOP instruction has been de-activated. Any attempt to execute a STOP will cause the automatic execution of a WAIT instruction.

### Exit from WAIT Mode

The following paragraphs describe the output procedure of the ST638x Core from WAIT mode when an interrupt occurs. It must be noted that the restart

sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) before the start of the WAIT sequence, but also of the type of the interrupt request that is generated. In all cases the GEN bit of IOR has to be set to 1 in order to restart from WAIT mode. Contrary to the operation of NMI in the RUN mode, the NMI is masked in WAIT mode if GEN=0.

Normal Mode. If the ST638x Core was in the main routine when the WAIT instruction has been executed, the ST638x Core outputs from the wait mode as soon as any interrupt occurs; the related interrupt routine is executed and at the end of the interrupt service routine the instruction that follows the WAIT instruction is executed if no other interrupts are pending.

Non-maskable Interrupt Mode. If the WAIT instruction has been executed during the execution of the non-maskable interrupt routine, the ST638x Core outputs from the wait mode as soon as any interrupt occurs: the instruction that follows the WAIT instruction is executed and the ST638x Core is still in the non-maskable interrupt mode even if another interrupt has been generated.

Normal Interrupt Mode. If the ST638x Core was in the interrupt mode before the initialization of the WAIT sequence, it outputs from the wait mode as soon as any interrupt occurs. Nevertheless, two cases have to be considered:

- If the interrupt is a normal interrupt, the interrupt routine in which the WAIT was entered will be completed with the execution of the instruction that follows the WAIT and the ST638x Core is still in the interrupt mode. At the end of this routine pending interrupts will be serviced in accordance to their priority.

- If the interrupt is a non-maskable interrupt, the non-maskable routine is processed at first.

Then, the routine in which the WAIT was entered will be completed with the execution of the instruction that follows the WAIT and the ST638x Core is still in the normal interrupt mode.

# Notes:

If all the interrupt sources are disabled, the restart of the MCU can only be done by a Reset activation. The Wait instruction is not executed if an enabled interrupt request is pending. In the ST638x the hardware activated digital watchdog function is present. As the watchdog is always activated the STOP instruction is de-activated and any attempt to execute the STOP instruction will cause an execution of a WAIT instruction.

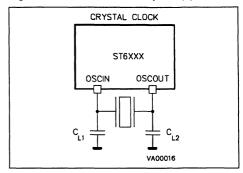

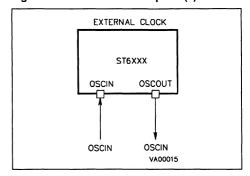

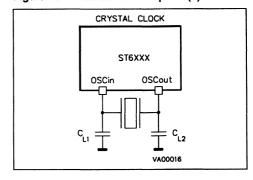

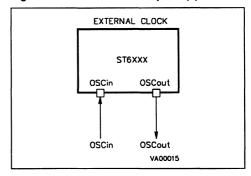

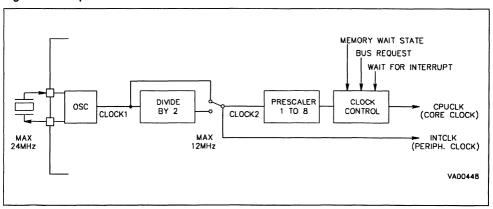

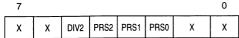

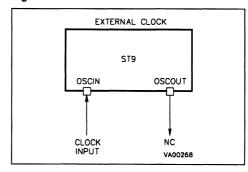

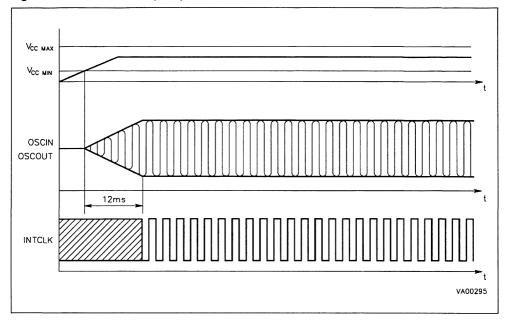

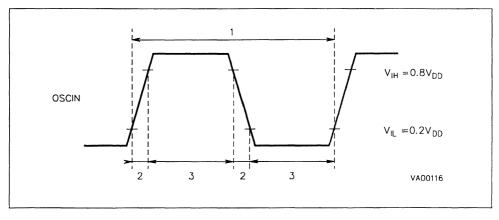

## **ON-CHIP CLOCK OSCILLATOR**

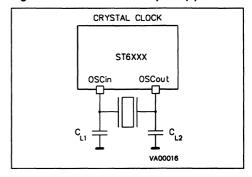

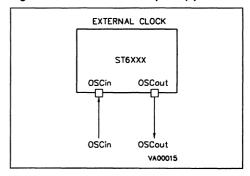

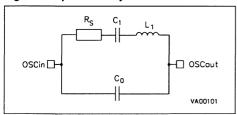

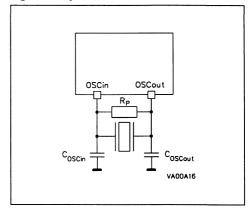

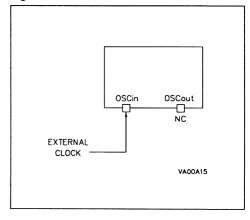

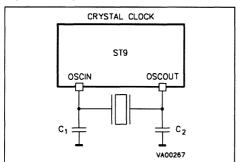

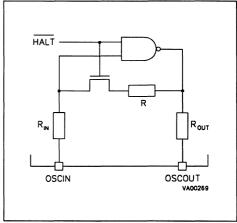

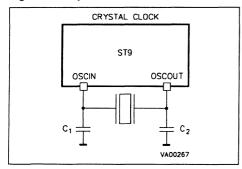

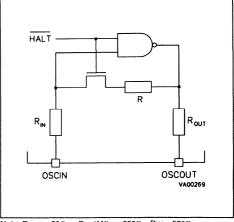

The internal oscillator circuit is designed to require a minimum of external components. A crystal quartz, a ceramic resonator, or an external signal (provided to the OSCin pin) may be used to generate a system clock with various stability/cost tradeoffs. The typical clock frequency is 8MHz. Please note that different frequencies will affect the operation of those peripherals (D/As, SPI) whose reference frequencies are derived from the system clock.

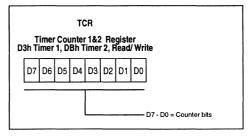

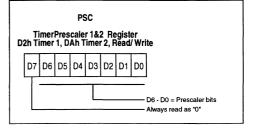

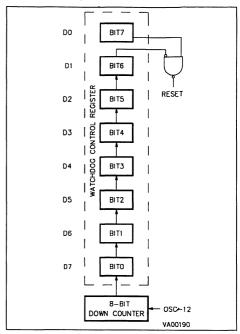

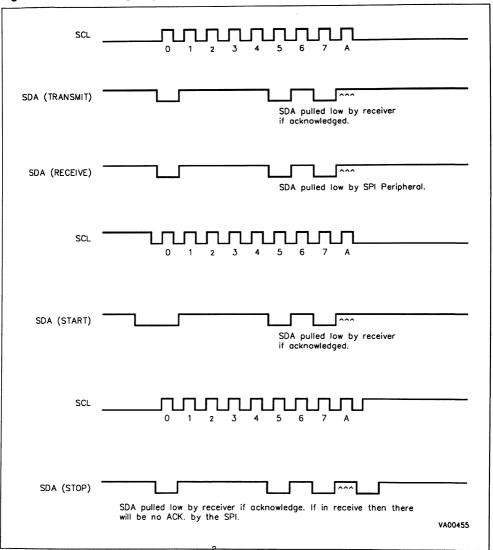

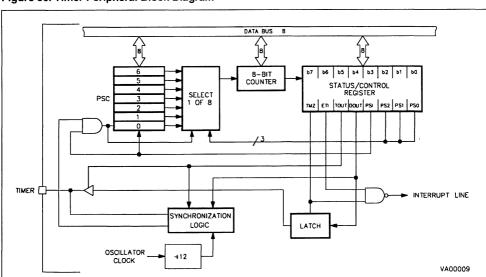

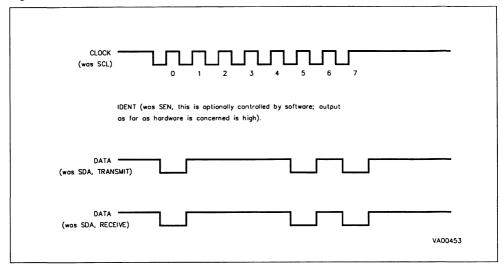

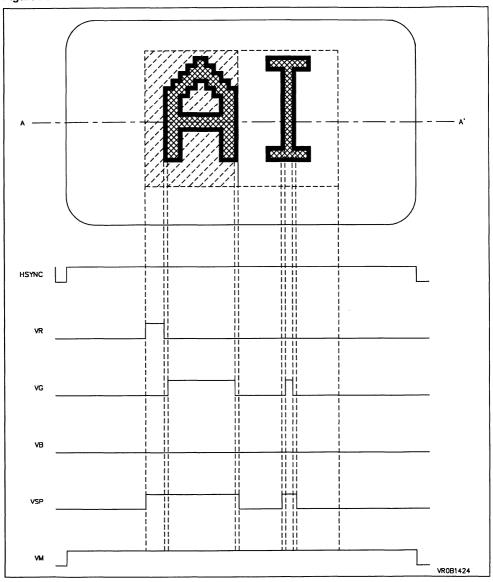

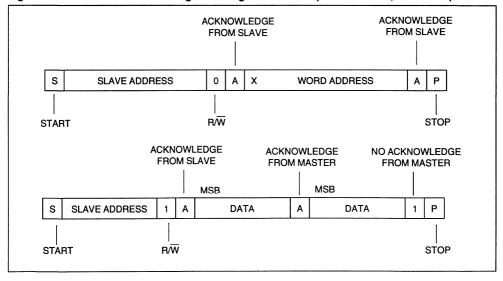

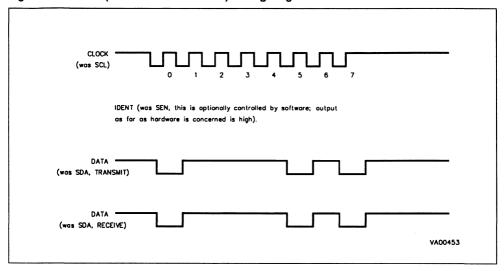

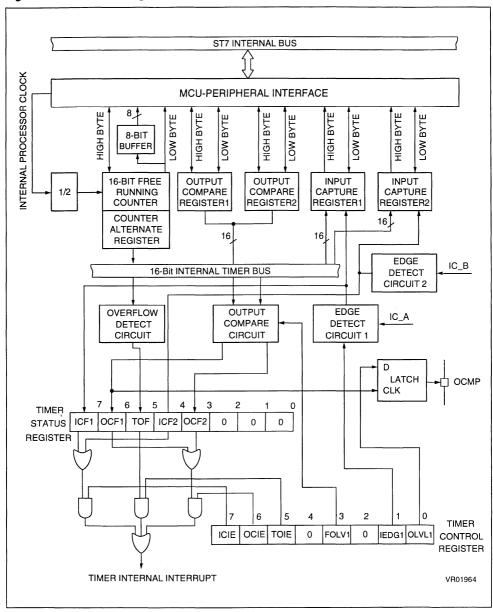

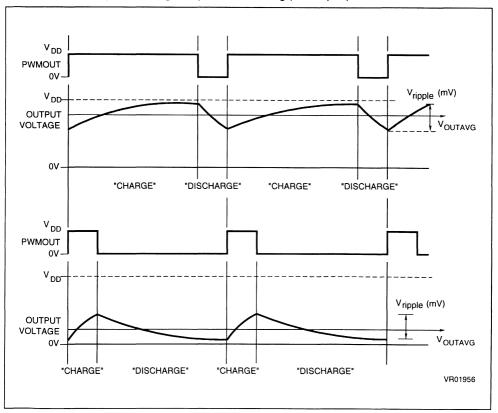

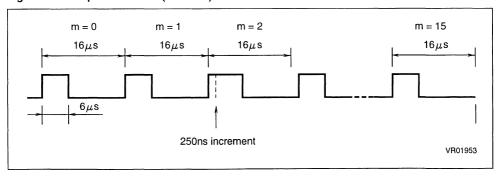

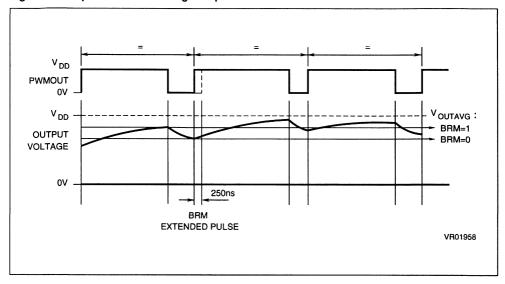

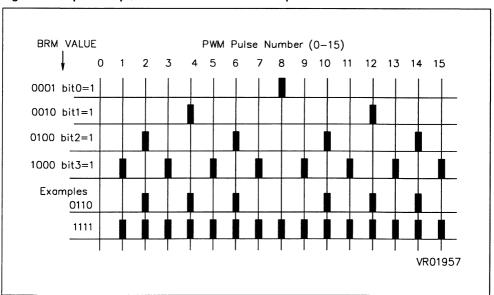

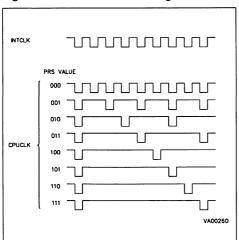

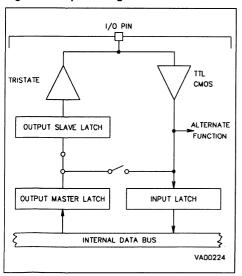

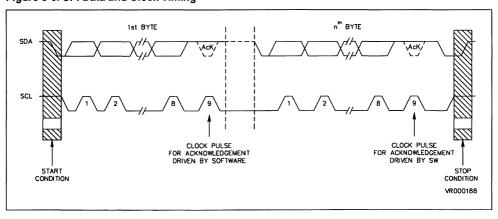

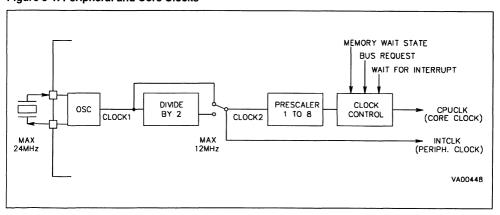

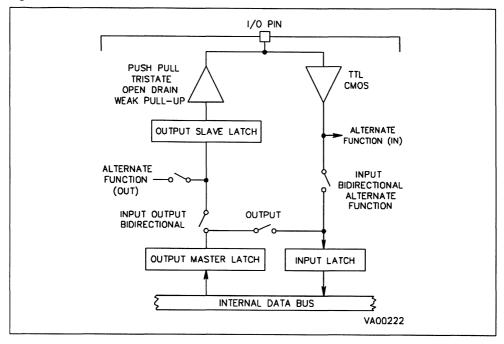

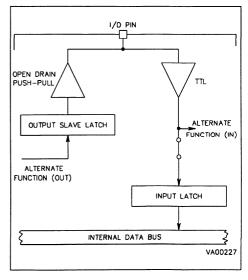

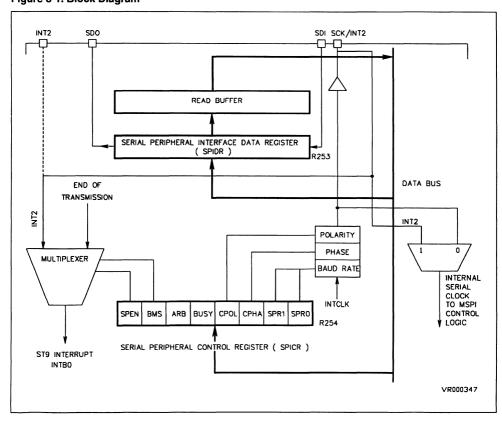

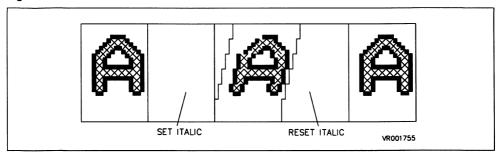

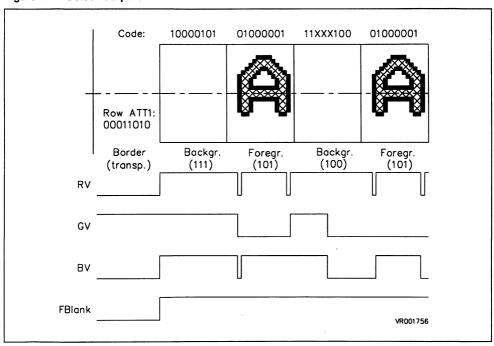

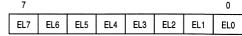

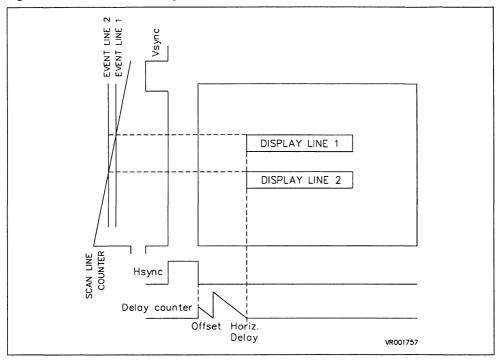

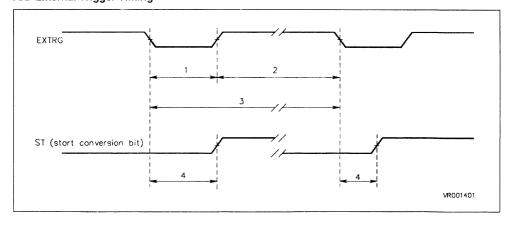

The different clock generator options connection methods are shown in Figures 24 and 25. One machine cycle takes 13 oscillator pulses; 12 clock pulses are needed to increment the PC while and additional 13th pulse is needed to stabilize the internal latches during memory addressing. This means that with a clock frequency of 8MHz the machine cycle is 1.625µs.